**International Journal of Engineering & Technology**

Website: www.sciencepubco.com/index.php/IJET

Research paper

# MATLAB/simulink study of multi-level inverter topologies using minimized quantity of switches

B.Vijaya Krishna<sup>1\*</sup>, B.Venkata Prashanth<sup>2</sup>, P.Sujatha<sup>3</sup>

<sup>1</sup>Assistant Professor, Department of EEE, Bapatla Engineering College <sup>2</sup>Professor & Head, Department of EEE, QIS CET, Ongole <sup>3</sup>Professor, Department of EEE, JNTUA,, Ananthapur \*Corresponding author E-mail: bvijayakrishna85@gmail.com

# Abstract

Multilevel Inverters (MLI) have very good features when compared to Inverters. But using more switches in the conventional configuration will reduce its application in a wider range. For that reason a modified 7-level MLI Topology is presented. This new topology consists of less number of switches that can be reduced to the maximum extent and a separate gate trigger circuit. This will reduce the switching losses, reduce the size of the multilevel inverter, and cost of installation. This new topology can be used in Electrical drives and renewable energy applications. Performance of the new MLI is tested via. Total harmonic distortion. This construction structure of this multilevel inverter topology can also be increased for 9-level, 11-level and so on and simulated by the use of MATLAB/SIMULINK. A separate Carrier Based PWM Technique is used for the pulse generation in this configuration.

Keywords: Multilevel Inverter, Conventional Cascaded MLI, PWM, Level Shifting PWM.

# 1. Introduction

Multilevel Inverters (MLIs) can be used in medium and high voltage applications for example in renewable energy sources, industrial drives, blowers, fans, laminators and conveyor systems. Small voltage steps in MLIs results in withstanding proficient voltage, minimal harmonics, enhances the electro-magnetic compatibility, eliminated the on/off losses, and excellent power quality [1-7].

Cascaded MLIs, Diode-Clamped MLIs, Flying Capacitor MLIs are the different types of MLIs types that have been developed so far. It is mentioned that simplicity is the main advantage of the Cascaded MLI. But increase in levels will increase the number of switches. Hence it is a contradictory in case of Cascaded MLI. Then arises the concept of "switch reduction". So Cascaded Multilevel Inverter has undergone many researches and still new trends have been introduced in the evolution of renewed Multi level inverters. Cascaded CMLI consists of 12 switches for getting 7-level output. Later 9-switch 7-level topology is introduced by eliminating three power ON/OF devices from the main Conventional CMLI. Then the configuration has been modified by reducing another 2 switches hence getting 7-switch 7-level configuration. And on later another new topology is constructed by reducing one switch that is 6-switch 7-level topology [8-15].

For the concept of decreasing the switches to optimal likely extent and suppressing the difficulty, a new topology is presented using five switches. This is the least possible reduction for a 7-level MLI. This 5-switch 7-level topology is a special arrangement with 4-DC input voltage sources.

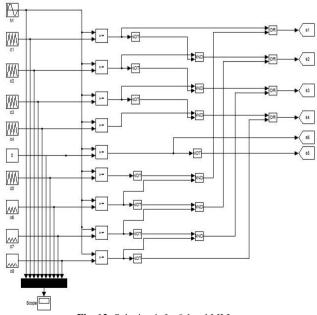

Decrease in the quantity of switches will suppress the on/off losses and the cost of the circuit construction is also reduced. The performance of the designed model is verified by various fixed switching Frequency PWM i.e PD, POD, APOD PWM techniques using MATLAB/SIMULINK.

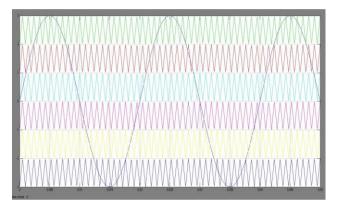

# 2. Level shifting carrier based PWM

PWM technique is applied for the purpose of Pulse generation. Among all the PWM techniques Carrier-Based technique is the easy one. It is again divided into Level and Phase shifting CBPWM's. Phase shifting CBPWM generates large harmonics when compared to the Level shifting CBPWM. Hence, Level Shifting CBPWM is applied in this designed system for pulse generation. This Level shifting CBPWM is again divided into 3 types [16-19]. They are

## A. Phase disposition PWM

In this PWM technique, N-1 carrier signals are used for the generation of N output voltage levels. All the carrier signals are equal in magnitudes, having same frequency and are in phase. In this PWM method, sine reference signal is compared with the vertically shifted triangular carrier signal.

## **B.** Phase opposition disposition PWM

In this POD PWM method, entire triangular carrier signals upward the origin axis is having the same frequency/ amplitude and in phases with one each other. In the same way, the entire carrier signals downward the origin axis is having the same frequency/magnitude and all are in phase with each other. Still, the carrier signals upward the origin axis is phase shifted by 180 degrees when compared to the carrier signals downward the origin axis.

# C. Alternative phase opposition disposition PWM

APOD PWM method, entire triangular carrier signals are having the same/amplitude. Hence, each and every carrier signal is shifted by phase of 180 degrees when compared to each other.

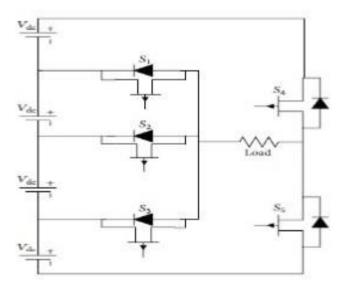

# 3. Proposed 5-switch 7-level topology

This 5-switch 7-level topology is the redesigned structural configuration of the six switch topology by removing one switch reaching the five switch model. Compared to the conventional configuration and existing topologies, this 5-switch structure is the simplest design. This topology consists of 4 DC input voltage sources for 7 levels, 5 DC input voltage sources for 9-levels and 6 DC input voltage sources for 11 levels and so on.

The General expression for level number of output voltage is

L=(2\*S-3), Where L=no.of o/p voltage levels S=no.of switches L=(2\*Vdc-1)

Where Vdc=no.of DC Input Voltage sources

sole pulse pattern of triggering the switches at proper instants, the design of PWM generation makes the circuit differ from other topologies. In this configuration, switches S1, S2, S3 must be unidirectional in order to avoid the distortions in the output waveform. Reducing the number of switches will make the circuit user friendly and compact. Switch reduction benefits in the lowering of switching losses. In this configuration H-Bridges are not used. The switches S4 and S5 are used for the purpose of polarity reversal. In Table-1 switching operations of switches are mentioned by 0 and 1. 0 indicates OFF state and 1 indicates ON state.

Fig. 1: 5-Switch 7-Level Topology

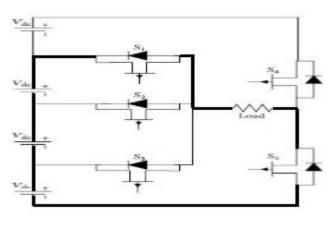

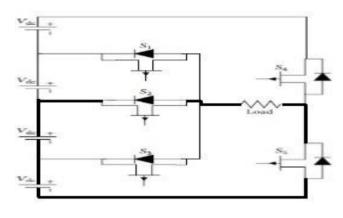

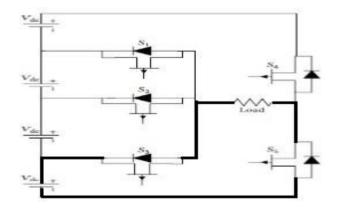

#### A. Modes of Operation

Mode-2

state-4

state-6

state-7

Table 1: Switching Topology of 5-Switch 7-Level MLI

| Sl.No | <b>S1</b> | S2 | <b>S</b> 3 | <b>S4</b> | <b>S</b> 5 | o/p<br>Voltage |

|-------|-----------|----|------------|-----------|------------|----------------|

| а     | 0         | 0  | 1          | 0         | 1          | +1Vdc          |

| b     | 0         | 1  | 0          | 0         | 1          | +2Vdc          |

| с     | 1         | 0  | 0          | 0         | 1          | +3Vdc          |

| d     | 0         | 0  | 0          | 0         | 0          | 0              |

| e     | 1         | 0  | 0          | 1         | 0          | -1Vdc          |

| f     | 0         | 1  | 0          | 1         | 0          | -2Vdc          |

| g     | 0         | 0  | 1          | 1         | 0          | -3Vdc          |

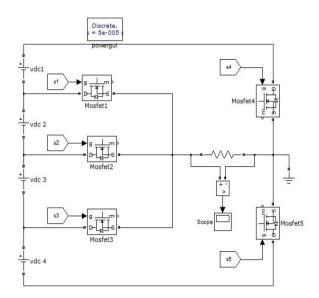

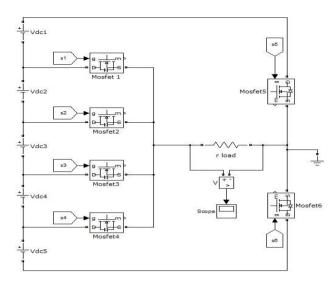

# 4. Simulation circuit

B. 5-Switch 7-Level MLI

The new topology circuit of 7-level MLI is constructed by the use of 5 MOSFET switches and 4 DC voltage sources. Among these 5-Mosfet Switches, 3- MOSFET switches are connected in between the 4 DC voltage sources and the remaining 2- MOSFET switches are used for the polarity reversal mechanism. Each DC input voltage values are 10V DC. Here Resistive load is used whose value is 100hms. The MOSFET block parameters are

FET resistance=0.01 Ohms Internal diode resistance = 10 Kilo Ohms.

Fig. 2: Simulation circuit for 5-Switch 7-Level Topology

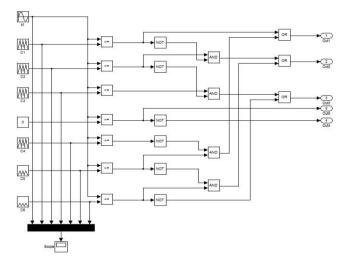

Fig. 3: Sub Circuit for 7-level MLI

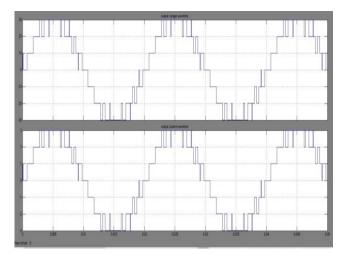

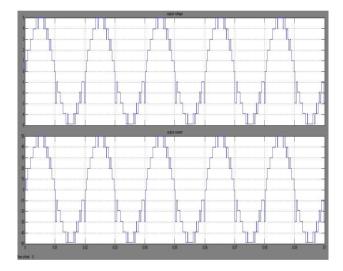

Fig. 4: Output voltage and current waveforms for 7-level MLI

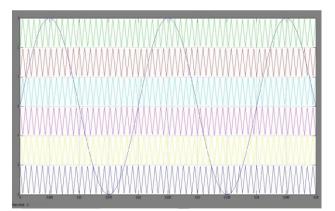

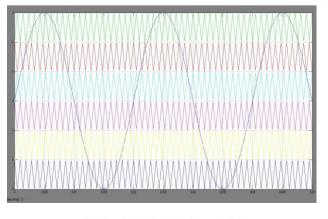

Fig. 5: PD PWM for 7-Level MLI

Fig. 6: POD PWM for 7-level MLI

Fig. 7: APOD PWM for 7-level MLI

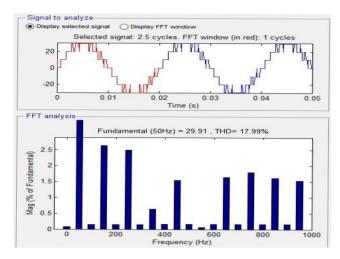

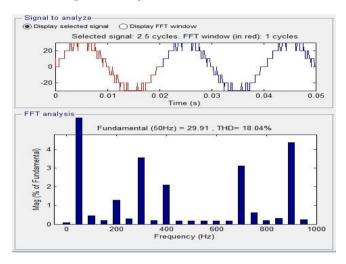

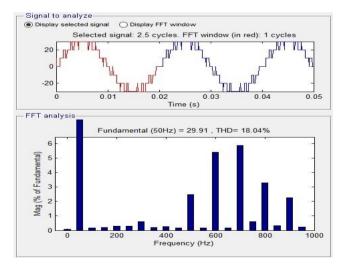

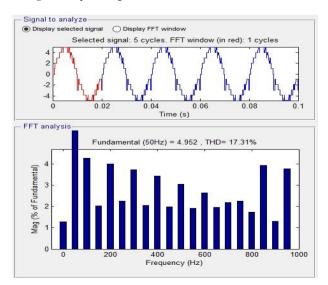

Fig. 9: FFT Analysis for POD PWM of 7-level MLI

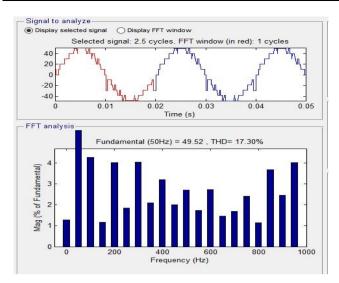

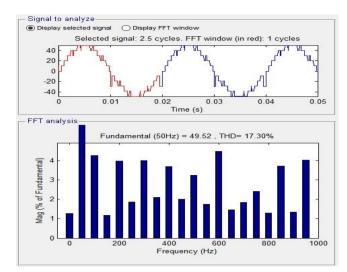

Fig. 10: FFT Analysis for APOD PWM of 7-level MLI

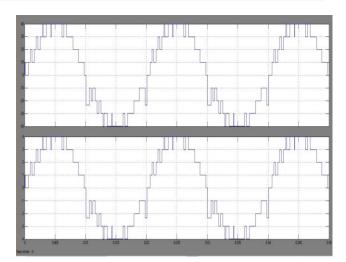

#### C. 6-Switch 9-Level MLI

This topology is also constructed in the same configuration of 5switch 7-level MLI. In this we use 5 DC voltage sources and 6 MOSFET switches. In this also 4 MOSFET switches are connected in between the 5 DC voltage sources and the remaining 2 MOSFETs play the role of Polarity reversal. The DC input voltage is 10V dc and the load used is a Resistive load whose value is 10 Ohms. MOSFET block parameters are same as the 5switch 7-level topology. In Table-2 switching operations of switches are mentioned by 0 and 1. 0 indicates OFF state and 1 indicates ON state.

Fig. 11: Simulation Circuit of 6-switch 9-level MLI

| Sl.no | <b>S1</b> | S2 | <b>S</b> 3 | <b>S4</b> | <b>S</b> 5 | <b>S6</b> | o/p<br>voltage |

|-------|-----------|----|------------|-----------|------------|-----------|----------------|

| а     | 0         | 0  | 0          | 1         | 0          | 1         | +1Vdc          |

| b     | 0         | 0  | 1          | 0         | 0          | 1         | +2Vdc          |

| с     | 0         | 1  | 0          | 0         | 0          | 1         | +3Vdc          |

| d     | 1         | 0  | 0          | 0         | 0          | 1         | +4Vdc          |

| e     | 0         | 0  | 0          | 0         | 0          | 0         | 0              |

| f     | 1         | 0  | 0          | 0         | 1          | 0         | -1Vdc          |

| g     | 0         | 1  | 0          | 0         | 1          | 0         | -2Vdc          |

| h     | 0         | 0  | 1          | 0         | 1          | 0         | -3Vdc          |

| i     | 0         | 0  | 0          | 1         | 1          | 0         | -4Vdc          |

Fig. 12: Sub circuit for 9-level MLI

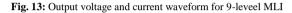

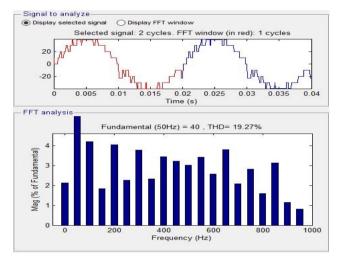

Fig. 15: FFT analysis for 9-level POD PWM

Fig. 16: FFT Analysis for 9-level APOD PWM

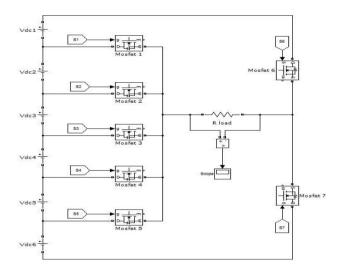

## D. 7-Switch 11-Level MLI

In this circuit 7 MOSFET switches and 6 DC voltage sources are used. 5 MOSFET switches are connected between the 6 DC voltage sources and the remaining 2 switches are used for the polarity reversal. MOSFET block parameters are the same as the above configuration. In Table-3 switching operations of switches are mentioned by 0 and 1. 0 indicates OFF state and 1 indicates ON state.

| Sl.no  | <b>S1</b> | S2 | <b>S</b> 3 | S4 | S5 | S6 | S7 | o/p     |

|--------|-----------|----|------------|----|----|----|----|---------|

| Sillio |           | ~- |            | 5. | 50 | 20 | 5. | voltage |

| а      | 0         | 0  | 0          | 0  | 1  | 0  | 1  | +1Vdc   |

| b      | 0         | 0  | 0          | 1  | 0  | 0  | 1  | +2Vdc   |

| с      | 0         | 0  | 1          | 0  | 0  | 0  | 1  | +3Vdc   |

| d      | 0         | 1  | 0          | 0  | 0  | 0  | 1  | +4Vdc   |

| e      | 1         | 0  | 0          | 0  | 0  | 0  | 1  | +5Vdc   |

| f      | 0         | 0  | 0          | 0  | 0  | 0  | 0  | 0       |

| g      | 1         | 0  | 0          | 0  | 0  | 1  | 0  | -1Vdc   |

| h      | 0         | 1  | 0          | 0  | 0  | 1  | 0  | -2Vdc   |

| i      | 0         | 0  | 1          | 0  | 0  | 1  | 0  | -3Vdc   |

| j      | 0         | 0  | 0          | 1  | 0  | 1  | 0  | -4Vdc   |

| k      | 0         | 0  | 0          | 0  | 1  | 1  | 0  | -5Vdc   |

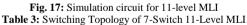

Fig. 18: Sub circuit for 11-Level MLI

Fig. 19: Output voltage and current waveforms for 11-level MLI

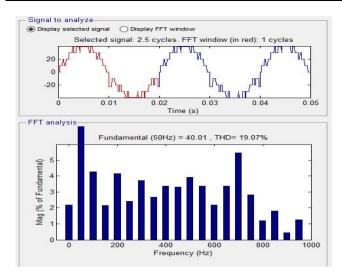

Fig. 20: FFT Analysis for PD PWM of 11-levelMLI

Fig. 21: FFT analysis for POD PWM of 11-level MLI

Fig. 22: FFT Analysis for APOD PWM of 11-level MLI

Table 4: Comparison of Proposed MLI With other MLI's

| Inbuilt Structure | Flying Capacitor | Diode<br>Clamped | Cascaded<br>7-level | 7-level 9-<br>switch | 7-level<br>7-switch | 7-level 6-<br>switch | 7-level 5-<br>switch |

|-------------------|------------------|------------------|---------------------|----------------------|---------------------|----------------------|----------------------|

| No.of Capacitors  | 14               | 6                | -                   | -                    | -                   | -                    | -                    |

| No.of Diodes      | -                | <u>≥</u> 8       | -                   | -                    | -                   | -                    | -                    |

| No.of Switches    | 10               | 10               | 12                  | 9                    | 7                   | 6                    | 5                    |

| No.of Sources     | -                | -                | 3                   | 3                    | 3                   | 4                    | 4                    |

Table 5: THD of 7-Level,9-Level,and 11-Level MLI"S

| PWM       | 5-switch 7- | 6-switch 9- | 7-switch 11-level |

|-----------|-------------|-------------|-------------------|

| Technique | level       | level       |                   |

| PD PWM    | 17.99       | 18.04       | 18.04             |

| PD PWM    | 19.27       | 19.22       | 19.07             |

| PD PWM    | 17.31       | 17.30       | 17.30             |

# 5. Conclusion

New topology of 7-level 5-switch MLI is successfully studied by the simulation circuit using MATLAB/SIMULINK. 9-level and 11-level MLI's are also executed by the use of above topology. Effectiveness of the topologies are studied by using THD. This new topologies are simple in design and operation when compared to other MLI structures. Switching losses for 7-level, 9level and 11-level MLI's are also very less when compared to other topologies.

# References

- J. Rodr'iguez, J.-S. Lai, and F. Z. Peng, "Multilevel inverters: a survey of topologies, controls, and applications," IEEE Transactions on Industrial Electronics, vol. 49, no. 4, pp. 724– 738, 2002.

- [2] Mohan and S. B. Kurub, "Performance analysis of SPWM control strategies using 13 level cascaded MLI," in IEEE International Conference on Advances in Engineering Science & Management (ICAESM '12).

- [3] O. L. Jimenez, R. A. Vargas, J. Aguayo, J. E. Arau, G. Vela, and A. Claudio, "THD in cascade multilevel inverter symmetric and asymmetric," in Proceedings of the IEEE Electronics, Robotics and Automotive Mechanics Conference (CERMA '11), pp. 289–295, November 2011.

- [4] P. Palanivel and S. S. Dash, "Analysis of THD and output voltage performance for cascaded multilevel inverter using carrier pulse width modulation techniques," IET Power Electronics, vol. 4, no. 8, pp. 951–958, 2011.

- [5] J. J. Nedumgatt, D. Vijayakumar, A. Kirubakaran, and S. Umashankar, "A multilevel inverter with reduced number of switches," in Proceedings of the IEEE Students' Conference on Electrical, Electronics and Computer Science (SCEECS '12), pp. 1–4, March 2012.

- [6] T. V. V. S. Lakshmi, N. George, S. Umashankar, and D. P. Kothari, "Cascaded seven level inverter with reduced numberof switches using level shifting PWM technique," in International Conference on Power, Energy and Control (ICPEC '13), pp. 676–680, February 2013.

- [7] R. A. Ahmed, S. Mekhilef, and H. W. Ping, "New multilevel inverter topology with minimum number of switches," in Proceedings of the 14th International Middle East Power Systems Conference (MEPCON '10), pp. 1862–1867, Cairo University, Cairo, Egypt, December 2010.

- [8] M. H. Rashid, Power Electronics: Circuits, Devices and Applications, Prentice Hall, New York, NY, USA, 3rd edition, 2004

- [9] Jacob James Nedumgatt, Vijayakumar D, A Kirubakaran, Umashankar S. A Multilevel Inverter with Reduced Number of Switches. IEEE Students' Conference on Electrical, Electronics and Computer Science. 2012.

- [10] Ebrahim Babaei. A Cascade Multilevel Converter Topology With Reduced Number of Switches. IEEE Trans. On Power electronics. 2008; 23(6): 2657- 2664.

- [11] Rodriguez, J.; Jih-Sheng Lai ; Fang Zheng Peng.—Multilevel inverters: a survey of topologies, controls, and applicationsl, IEEE Transactions on Industrial Electronics, vol. 49, no. 4, pp 724-738

- [12] Bahravar, S.; Babaei, E.; Hosseini, S.H.: New cascaded multilevel inverter topology with reduced variety of magnitudes of dc voltage sources. In: Proceedings of IICPE, Delhi, India (2012)

- [13] G.Bhuvaneshwari and Nagaraju "multilevel inverters a comparative study" vol .51 no.2 march april 2005.

- [14] J. Ebrahimi, E. Babaei, and G. B Gharehpetian, "A new topology of cascaded multilevel converters with reduced number of components for high voltage applications "IEEE Trans. Power Electron., vol.26, no. 11,pp. 3109–3118, Nov,2011.

- [15] José Rodríguez, "Multilevel Inverters: A Survey of Topologies, Controls, and Applications", IEEE Transactions On Industrial Electronics, Vol. 49, No. 4, August 2002

- [16] T V V S Lakshmi, Noby George, Umashankar S and Kothari D P "Cascaded seven level inverter with reduced number of switches "2013 International Conference on Power, Energy and Control (ICPEC).

- [17] S. Umashankar, T. S. Sreedevi, V. G. Nithya, and D. Vijayakumar "A New 7-Level Symmetric Multilevel Inverter with Minimum Number of Switches" ISRN Electronics Volume 2013, Article ID 476876.

- [18] K. Ramash Kumar, D. Kalyankumar, V. Kirubakaran,"An Hybrid Multi Level Inverter Based DSTATCOM Control," Majlesi Journal of Electrical Engineering, Vol.5, No. 2, pp. 17-22.

- [19] K. Ramash Kumar, S. Jeevananthan, "Analysis, Design and Implementation Of Hysteresis modulation sliding mode controller for negative output elementary boost converter", Journal of Electric Power Components and Systems, 40:3, 292-311, 2012

- [20] Rajesh, M., and J. M. Gnanasekar. "Path observationbased physical routing protocol for wireless ad hoc networks." International Journal of Wireless and Mobile Computing 11.3 (2016): 244-257.

- [21] S.V. Manikanthan and K.srividhya "An Android based secure access control using ARM and cloud computing", Published in: Electronics and Communication Systems (ICECS), 2015 2nd International Conference on 26-27 Feb. 2015, Publisher: IEEE, DOI:10.1109/ECS.2015.7124833.

- [22] T. Padmapriya and V. Saminadan, "Improving Throughput for Downlink Multi user MIMO-LTE Advanced Networks using SINR approximation and Hierarchical CSI feedback", International Journal of Mobile Design Network and Innovation-Inderscience Publisher, ISSN: 1744-2850 vol. 6, no.1, pp. 14-23, May 2015.