**International Journal of Engineering & Technology**

Website: www.sciencepubco.com/index.php/IJET

Research paper

# A Study on Electrical Characterization of Surface Potential and Threshold Voltage for Nano Scale FDSOI MOSFET

Chandra Shakher Tyagi<sup>1\*</sup>, R.L. Sharma<sup>2</sup>, Prashant Mani<sup>3</sup>

<sup>1, 2, 3</sup>Department of Electronics and Communication Engineering

<sup>1, 2</sup> Noida International University, Noida, U.P. INDIA

<sup>3</sup>SRM Institute of Science and Technology, U.P. INDIA

\*Corresponding Author E-mail: <sup>1\*</sup>tyagi\_shekhar@yahoo.co.in, <sup>2</sup>rlsharmadigudr@yahoo.co.in,

<sup>3</sup>prashant.m@ncr.srmuniv.ac.in

#### Abstract

In this paper the study of electrical characterization of Surface potential & Vth threshold-voltage model is developed for FD SOI MOSFET. The threshold voltage is important parameter in device design. Scaling of device has positive impact on device performance. The various parameters like thickness of silicon film, oxide layer, drain to source voltage plays a key role in improvement of device performance. Surface potential explain the distribution of applied potential throughout the channel. We also analyzed the effect of threshold voltage with various electrical parameters.

Keywords: Nano scale, Short-channel effects, silicon- on-insulator (SOI), channel length, 3-D, surface potential, MOSFET, Threshold voltage.

## 1. Introduction

Complementary Metal oxide semiconductor has been a radical invention in Very large scale industry field and serves as the main component of every electronics device (like mobile, computer, etc.) right from its inception [1-4]. For faster, cheaper and smaller size devices, it has been there in the eyes of researchers to trim down the device size below sub 50nm levels. But as the device minifies, the concern that arises is the degradation of the device performance with gradual decrease in channel length which are collectively called the SCEs [4]. This brings the new technology in play called the SOI [5]. The SOI technology is widely used in the semiconductor devices between channel and substrate. The SOI MOSFETs performance increases due to various reasons like reduced parasitic capacitances. The SOI MOSFETs are more advantageous in comparison to conventional due to no floating body effect present in device. The low leakage effect free from kink effect make the SOI devices more effective in comparison to conventional MOSFETs [11-13]. The channel of SOI MOSFET further classified as fully and partially depleted. In a Fully Depleted Silicon on Insulator Metal Oxide

Semiconductor Field Effect Transistor the Si substrate being very thin is fully depleted eliminating any floating body effect. The front and back gates (bulk Si below the insulator can be viewed as the second gate) are electro statically coupled. Unlike PDSOI,  $\Psi_{SF}$  is a function of  $\Psi_{SB}$ . Only the valence and conduction band edges are shown for simplicity. The Fully Depleted Silicon on Insulator is advantageous over partially depleted SOI MOSFET in terms of FD circuits are having low noise, very easy to design, floating body effect is low, kink effect is low as compared to PD circuits to suppress the effect of Scaling, which is responsible for device performance degradation.

Due to continuous minimization of physical device dimensions the conventional MOSFETs are stuck at performance aspects [9-10]. The SOI MOSFETs are different from conventional MOSFET in structural difference i.e. a layer of  $SiO_2$  is introduced.

### 2. SOI MOSFET Device Structure

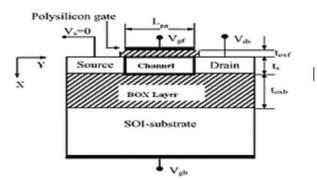

In comparison to conventional MOSFET, SOI MOSFET uses silicon insulator silicon substrate. On the basis of thickness of SOI (Silicon on Insulator) layer the MOSFET further categorized as Fully Depleted and Partially Depleted MOSFETS [7]. In partially Depleted SOI MOSFETs the thickness of insulator layer is kept more in comparison to depletion width of gate (50-100 nm).The main advantage over the conventional MOSFET are operated at low power, performance gain of 18-35%. In Fully Depleted SOI MOSFET as shown in figure[1] the channel is completely depleted via majority carriers as the silicon layer is thin (5-25nm). The advantage of fully depleted over partially depleted is to eliminate the floating point effect. Difference between FDSOI MOSFET and PDSOI MOSFETs has been shown in table 1(8).SOI MOSFET is also better than bulk-Si as it reduced the parasitic capacitance, short channel effects and can be used for simplifying the process.

| FDSOI MOSFET                | PDSOI MOSFET                          |

|-----------------------------|---------------------------------------|

| Thickness of Insulating BOX | Thickness of Insulating BOX is 90-200 |

| is 10-50 nm                 | nm                                    |

| Top Silicon layer is 5-25nm | Top Silicon layer is 50-100 nm        |

| It is used in low power     | It is used in analog circuits         |

| application                 |                                       |

| Easy to design              | Complex to design                     |

#### **3. Device Modeling**

Fig. 1: Cross Section View (x-y) of FDSOI MOSFET

$$\frac{\partial^2 \,\phi(xyz)}{\partial x^2} + \frac{\partial^2 \,\phi(xyz)}{\partial y^2} + \frac{\partial^2 \,\phi(xyz)}{\partial z^2} \tag{1}$$

The 3D Poisson's equation for Fully Depleted SOI MOSFET can be given by the equation[9] Here  $N_A$  represents the doping concentration and  $\emptyset(x, y, z)$  is the surface potential at point(x,y,z).The solution of Possion's equation with required boundary conditions [6] are given below as

$$\phi(0, y, z) - \frac{t_{oxf}}{\epsilon_{ox}} [\epsilon_{si} \frac{\partial \phi(x, y, z)}{\partial x}]_{x=0} - Q_{it}^{f}] = V_{gf} - V_{fb}^{f}$$

(2)

$$\emptyset(t_{si}, y, z) - \frac{t_{oxf}}{\epsilon_{ox}} [\epsilon_{si} \frac{\partial \emptyset(x, y, z)}{\partial x}]_{x=tsi+} Q^{b}_{it} = V_{gf-} V^{b}_{fb})$$

(3)

$$\phi(x,0,z) = V_{bi} \tag{4}$$

$$\emptyset(x, L_{EFF,} Z) = V_{bi} + V_{ds} \qquad (5)$$

$$\phi(x, y, 0) - \frac{t_{oxw}}{\epsilon_{ox}} [\epsilon_{si} \frac{\partial \phi(x, y, z)}{\partial x}]_{z=0} - Q_{it}{}^{f}] = V_{gf} - V^{f}{}_{fb}$$

(6)

$$\emptyset(x, y, w) + \frac{\tau_{oxw}}{\epsilon_{ox}} [\epsilon_{si} \frac{\partial \emptyset(x, y, z)}{\partial x}]_{z=w+} Q_{it}^{f}] = V_{gf} - V_{fb}^{f} \tag{7}$$

$$\frac{d^2 \, \vartheta l(x)}{dx^2} = \frac{q N_A x}{\epsilon_{si}} \tag{8}$$

$$\frac{d^2}{dx^2} \frac{\phi'(x,y)}{dy^2} + \frac{d^2}{dy^2} \frac{\phi'(x,y)}{dy^2} = 0$$

(9)

$$\frac{d^2}{dx^2} \phi''(x,y,z) + \frac{d^2}{dy^2} \phi''(x,y,z) + \frac{d^2}{dy^2} \phi''(x,y,z) + \frac{d^2}{dy^2} \phi''(x,y,z) = 0$$

(10)

## 4. Result and Discussion

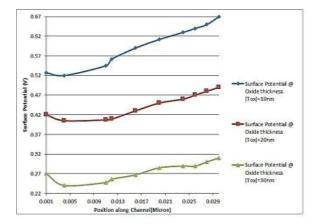

Fig. 2: Channel potential variation with normalized positionalong the channel length at Vds ~0.5~V

From figure The distribution of Surface potential inside the channel is represented at particular thickness of silicon layer, the distribution of surface potential also varies from source to drain terminals. The minimum surface potential is observed in the region

near to source terminal and maximum potential is observed in the region towards drain terminal.

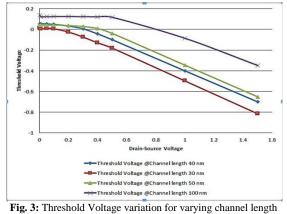

Figure describes the variations in threshold voltage with channel length along with  $V_{ds}$ , drain to source voltage, As we reduced the length of the channel , threshold voltages vary accordingly due to the electrons now require less distance.

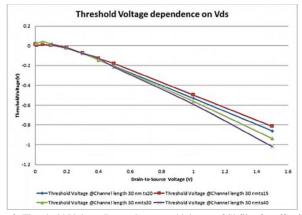

Fig. 4: Threshold Voltage Dependence on thickness of Si film for effective channel length 30nm and  $t_s$  15,20,30,40 nm

Figure describes the variations in threshold voltage with thickness of silicon layer along with  $V_{\rm ds},$  drain to source voltage, As we reduced the thickness of silicon layer , threshold voltages vary accordingly due to the increase in controlability of electron in channel and further reduced as drain to source to voltage increased.

#### 5. Conclusion

The effect of threshold voltage is prominent in increase of device performance. The length of the channel is another parameter which can be utilized to enhance the performance of the SOI MOSFET in nano scale range. The physical dimension of the device shrinks micrometer to nano meter and the device performance enhanced. In case of 100 nm , 50nm, 40nm,30nm channel length devices the device performance increased in terms of better threshold voltage of the SOI devices which is essential for low power consumption issues.

#### Reference

- Arora, N,"MOSFET models for VLSI Circuit Simulation", Wien New York, NY: springer Verlag, 1993.

- [2] Colinge, "silicon on Insulator technology: Materials to VLSI (2nd ed.)", Norwell, MA : Kluwer Academic Publishers, 1997.

- [3] Cristoloveanu, S. and Li, "S.S, Electrical characterization of SOI Devices, Norwell, MA: Kluwer Academy Publisher", 1995.

- [4] D.J. Frank, R.H. Dennard, E. Nowak ,P.M.Solomon, Y. Taur, and H.-S.P.Wong, "Device scalling limits of si MOSFETs and their Application dependencies," Proc.IEEE ,vol.89, no.3, pp.259-288, Mar.2001.

- [5] Current, M.I., Bedell, S.W., Malik, I.J., Feng, L.M., and Henley, F.J. "What is the future of sub—100nm CMOS : Ultrashallow Junctions or Ultrathin SOI?" Solid StateTechnology", 66-77, 2000.

- [6] Guruprasad Katti, Nandita Das Gupta and Amitava Das Gupta," Threshold voltage model for mesa isolated small geometry fully depleted SOI MOSFETs based on analytical solution of 3-D Poissions equation ",IEEE Trans. Electron Devices, vol.51, no.7, pp.1169-1177, July 2004.

- [7] F.Z. Rahou, M.Rahou and A. Guen Bouazza, "Study and Simulation of SOI n-MOSFET Transistor Single Gate using SILVACO Software", Global J.res. Eng. Electrical Electron. Eng. 13 No 1, Version 1.0(2013).

- [8] G.G. Shahidi et al., "Partially Depleted SOI Technology for Digital Logic,"1999 IEEE International Solid State Circuit Conference, Digest of Technical Papers,pp.426-427, Februray 1999.

- [9] Prashant Mani and M.K.Pandey, "Surface Potential and Threshold Voltage Model of Fully Depleted Narrow Channel SOI MOSFET Using Analytical Solution of 3D Poisson's Equation", Journal of Nano- and Electronic Physics vol.7, 2015.

- [10] Prashant Mani and M.K.Pandy, , "Simulation Analysis of Conduction in Ultra Thin Nano Scale Fully Depleted SOI MOSFET", International Journal of ChemTech Research, Vol.7 No. 2, pp.1014-1018.

- [11] Prashant Mani and M.K.Pandey, "Simulation Analysis of Narrow Width Effect in Nano Structured Fully Depleted SOI MOSFET", Procedia of computer science, vol.57, pp.637-641 2015.

- [12] Prashant Mani and M.K.Pandy, "Analytical Solution of 2d Poisson's Equation Using Separation of Variable Method for FDSOI MOSFET," International Journal of Electronics and Communication Engineering & Technology COMMUNICATION ENGINEERING & TECHNOLOGY (IJECET), November 2013, pp. 150-154.

- [13] Prashant Mani and Shivam Sharma "Analysis of Narrow Channel Single Gate Fully Depleted SOI MOSFET," International Journal of Engineering Research & Management Technology, Volume 2, Issue-2, March- 2015, pp. 140-145.