**International Journal of Engineering & Technology**

Website: www.sciencepubco.com/index.php/IJET

Research paper

# **Design of Low Delay Ring Oscillator Using CMOS**

S. Shiyamala<sup>1\*</sup>, T. Kavitha<sup>2</sup>

<sup>1</sup>Associate Professor, Department Of ECE, Veltech Rangarajan Dr.Sagunthala R&D Institute Of Science And Technology, Chennai. <sup>2</sup>Associate Professor, Department Of ECE, Veltech Rangarajan Dr.Sagunthala R&D Institute Of Science And Technology, Chennai.

E-Mail:Drkavitha@Veltech.Edu.In

\*Corresponding Author E-Mail:Drshiyamala@Veltech.Edu.In

#### Abstract

In the Era of digital World, low power applications are the needs of the market to save the resources. Delay elements (e.g. digital clock) are essential parts of such digital applications. Ring oscillators have been used because of their ease of implementation, wide tuning ranges, operating at low voltages and existing possibility of complete integration in standard CMOS processes. It desires at identifying the best possible configuration for the hoop oscillators having the least strength intake and precise delay with lesser sensitivity to the variations inside the temperature and deliver voltage for frequencies of few KHz. while N = 7, for 0.18 µm generation, put off is 0.07ns simplest. Compare with N = 3, 14.2 % delay time reduced and 12.6 % lower when N = 7 taken into account.

Keywords: Ring oscillator, transistor size, delay, chain stage.

## 1. Introduction

Power is more sufficient to operate the ring. When it crosses the required positive threshold voltage, oscillations start without any additional resources. To boom the frequency of oscillation. strategies are generally used; initially the implemented voltage can be increased. This increases both the frequency of the oscillation and the modern-day frenzied. The maximum permissible voltage implemented to the circuits limits the velocity of a given oscillator. Secondly, making the hoop from a smaller quantity of inverters consequences in a higher frequency of oscillation given certain electricity intake. due to the fact a single inverter computes the logical now not of its input, it may be shown that the remaining output of a series of an peculiar quantity of inverters is the logical not of the first enter. The very last output is declared a finite quantity of time after the primary enter is asserted and the feedback of the final output to the enter causes oscillation.

A round sequence composed of a truthful number of inverters cannot be used as a ring oscillator. The remaining output in this situation is the same as the input. However, this configuration of inverter remarks may be used as a garage detail and it is the number one constructing block of static random access memory or SRAM.

An excessive-velocity ring oscillator is proposed for stepped forward operation frequency over those primarily based on the traditional n-stage inverter chain. The ring oscillator includes inverters with bad postpone elements which can be derived from the ring oscillator circuit. The mobile delay of the ring oscillator is smaller than a fundamental inverter delay. Simulations show that the ensuing working frequencies are 50% better than the ones available from the conventional tactics.[1-5]

Physically supported evaluation illustrated the noise strategies in CMOS inverter-for single ended and differential ended ring

oscillators. A time-area jitter calculation technique is used to analyze the consequences of white noise, whilst random VCO modulation maximum straightforwardly owed for flicker noise. [6-12] analysis shows that during differential ring oscillators, white noise in the differential pairs dominates the jitter and phase noise, whereas the section noise because of flicker noise arises especially from the tail contemporary, manage circuit. This is tested by simulation and dimension. Honest expressions for duration jitter and phase noise permit manual layout of a hoop oscillator to specs, and manual the selection among ring and LC oscillator.

A layout that gives every of those tendencies is the saturated advantage diploma with regenerative pass-coupled PMOS transistors [5]. This offers for rail-to-rail output signals and entire switching of the FETs within the degree. From a qualitative factor of view, it is able to be visible that the feedback residences of the latching transistors BJT1 and BJT2 to improve the signal transitions on the output. The extent additionally avoids the usage of cascode connections and a tail contemporary-source transistor that would restrict the signal swing and upload greater noise to the output.

## 2. Ring Oscillator - Working Principle

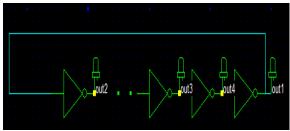

Fig. 1: Inverter chain to form ring oscillator

Copyright © 2018 Authors. This is an open access article distributed under the <u>Creative Commons Attribution License</u>, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Oscillatory behavior is mandatory in all communication systems, microprocessor and embedded system. In radio frequency and light wave verbal exchange structures, oscillators are used for frequency translation of statistics signals and channel selection.

Digital domain mainly utilizes the oscillators, with the help of the generation of clock signals, synchronization operation will happen in a smoother way. An ideal oscillator might offer a great time reference, i.e, a periodic sign. Noise generation in physical oscillators creates a greater problem in analog circuits. Consequently indicators generated by realistic oscillators aren't flawlessly periodic, when you consider that oscillator is a noisy bodily gadget and it makes them unique of their reaction to perturbation/noise.

#### 3. Low Noise Ring Oscillator - Constraints

Design hassle is a big capacitive load without immoderate delay, locality and strength necessities. Large size power backup is required to power the capacitive load at the very least degree. Due to the fact the gate capacitance of an inverter is proportional to its duration; a medium period inverter is required to stress the huge inverter. Consequently, series of inverters are connected with small variation in aspect ratio will give a better result. [13]. If the number of stages get increased, signal strength become too weak. But, if the number of stages chosen too short also generate serious problem in the output wave, that is signal inclined to zero slowly. This project dealt carefully related with number of stages by experimentally. Channel length and aspect ratio get varied for each condition and repeat the same for all stages. To simplify the layout evaluation, regularly recuperation the degree ratio of the inverter chain to a steady state. Because of this the number one inverter has a unit length (typically the smallest length), the second has length ok, the 1/3 has length K2, and many others. For extra superior designs, an automated-gain-managed amplifier is used to provide higher voltage swing control, oscillation stability and method version tolerance. Notwithstanding the fact that a low gain amplifier is good for strength dissipation, it does lengthen the start-up time of the oscillator circuit.

- (i) 0.18μm Technology Seven Stages Aspect Ratio N1 = 1.8μm for NMOS, 3.6 μm for PMOS N2 = 3.6μm for NMOS, 5.2μm for PMOS N3 = 5.2μm for NMOS, 10.4 μm for PMOS N4 = 10.4μm for NMOS, 20.8 μm for PMOS N5 = 20.8μm for NMOS, 41.6 μm for PMOS N6 = 41.6μm for NMOS, 83.2μm for PMOS N7 =83.2μm for NMOS, 166.4μm for PMOS

(ii) 0.25μm Technology – Seven Stages – Aspect Ratio

- (ii) 0.25µm fechnology Seven Stages Aspect Rat N1 = 2.5µm for NMOS , 5 µm for PMOS N2 = 5µm for NMOS , 10µm for PMOS N3 = 10µm for NMOS , 20 µm for PMOS N4 = 20µm for NMOS , 40 µm for PMOS N5 = 40µm for NMOS , 80 µm for PMOS N6 = 80µm for NMOS , 160µm for PMOS N7 = 160µm for NMOS , 320µm for PMOS

- (iii) 0.32µm Technology Seven Stages Aspect Ratio N1 = 3.2µm for NMOS, 7.2 µm for PMOS N2 = 7.2µm for NMOS, 15.4µm for PMOS N3 = 15.4µm for NMOS, 30.8 µm for PMOS N4 = 30.8µm for NMOS, 61.6 µm for PMOS N5 = 61.6µm for NMOS, 123.2 µm for PMOS N6 = 123.2µm for NMOS, 246.4µm for PMOS N7 =246.4µm for NMOS, 492.8µm for PMOS

#### 4. Result and Discussion

Micro wind is a tool for designing and simulating circuits at format stage. The device features full enhancing facilities (copy, reduce, beyond, replica, pass), numerous views (MOS traits, 2nd pass phase, 3D technique viewer), and an analog simulator. DSCH is a software program for common sense layout. Based totally on primitives, a hierarchical circuit may be built and simulated. It is also postpone and energy consumption assessment. Silicon is for 3-D show of the atomic shape of silicon, with emphasis at the silicon lattice, the dopants, and the silicon dioxide. The oscillation frequency of an RO relies upon on the propagation put off of the inverter stages. The smallest propagation put off time is decided by way of the structure of the inverter stage, method parameters and design technology and it may be expanded by using incorporating additional voltage manage delay (may be capacitive or resistive-capacitive load) on the output of the inverter level.

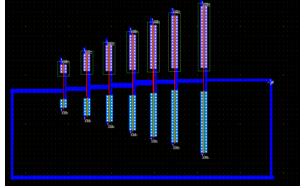

Fig. 2: 0.18µm technology – seven stages– schematic diagram

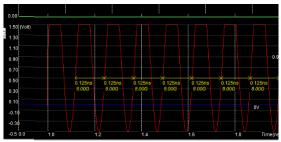

Fig. 3: 0.18 µm technology seven stages -frequency vs time

| Table 1: Delay Calculation for various stages in Ring Oscillator |                  |          |          |          |

|------------------------------------------------------------------|------------------|----------|----------|----------|

| Technology                                                       | 3 Stages         | 5 Stages | 7 Stages | 9 Stages |

|                                                                  | Noise delay (ns) |          |          |          |

| 0.18µm                                                           | 0.1              | 0.09     | 0.07     | 0.09     |

| 0.25µm                                                           | 0.08             | 0.07     | 0.05     | 0.06     |

0.01

0.04

0.05

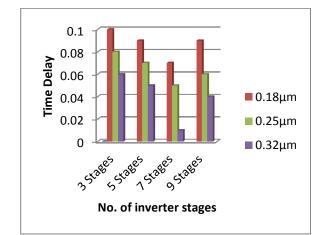

Fig. 4: Comparison chart for delay calculation for various stages in Ring Oscillator

## 5. Conclusion

0.32um

0.06

Ring oscillators are fundamental building blocks of complicated incorporated circuits. They are specifically used as clock producing circuits. They fluctuate in appreciate to architectural, cognizance of inverters stages, number of inverter stages, etc. According to the obtained simulation results jitter of ring oscillator depends upon the number of stages taken in to account. When number of stages gets low also delay value becomes high, similarly stages increasing also face the same problem. Optimized state only has a lower delay. Here stage seven provides better results.

### References

- Ashish R, Jaya NV & Sarin RK, "A RF Low Power 0.18-µm based CMOS Differential Ring Oscillator", World Congress on Engineering, (2012).

- [2] Bell A & Borriello G, "A single chip nMOS Ethernet controller", *IEEE International Solid-State Circuits Conference (ISSCC)*, (1983).

- [3] Behzad R, *Design of Analog CMOS Integrated Circuit*, Tata McGraw Hill pvt ltd, Edition, (2002).

- [4] Bijvendra R, "A Voltage Controlled Oscillator using Ring Structure in CMOS Technology", *International Journal of Electronics and Computer Science Engineering*, (2012).

- [5] Chetan SS, *Design of cmos LC voltage Controlled oscillators*, Visveswariah Technological University, India, (2006).

- [6] Cua ZY, "Comparative study of low phase noise voltage controlled oscillator (VCOs) CMOS Technology, Concordia University, Montreal, Quebec, Canada, (2006).

- [7] Lee YH, Chuang SLJ & Chen CC, "Low phase noise IEEE Microwave and Wireless Components Letters", *IEEE Microwave* and Wireless Components Letters, Vol.17, No.2, (2007), pp.145–147.

- [8] Mohammad NG, "A Low Power Low Phase CMOS Voltage Controlled Oscillator", 17th IEEE International Conference on Electronics, Circuits, and Systems (ICECS), (2010).

- [9] Nandanwar MA & Gaikwad DD, "Low Power Low Phase Noise CMOS LC VCO-A Review", *International Journal of Applied Information Systems (IJAIS)*, Vol.3, (2012), pp.37–41.

- Information Systems (IJAIS), Vol.3, (2012), pp.37–41.

[10] Pie L, Jo YF, Robert JW, "A 2.4 GHz Low- Power Low-Phase Noise CMOS LC VCO", VLSI, IEEE Annual Symposium on computer Society (2004), pp.213-214.

- [11] Samori C, Levantino S & Boccuzzi V, "A-94 dBc/Hz@ 100 kHz, fully-integrated, 5-GHz, CMOS VCO with 18% tuning range for Bluetooth applications", *IEEE Conference on Custom Integrated Circuits*, (2001), pp.201-204.

- [12] Wang JAH, "A 5 GHz differential Colpitts CMOS VCO using the bottom PMOS cross couple current source", *IEEE Microwave and Wireless Components Letters* Vol.19, No.6, (2009), pp.401–403.

- [13] Yeap GK, *Practical low power digital VLSI design*. Springer Science & Business Media, 2012.