International Journal of Engineering & Technology

Website: www.sciencepubco.com/index.php/IJET

Research paper

# **Comparative Analysis of High Speed Carry Skip Adders**

Ch. Naga Babu<sup>\*</sup>, P. Naga Siva Sai, Ch. Priyanka, K. Hari Kishore, M.Bindu Bhargavi, K.Karthik

Department of ECE, Koneru Lakshmaiah Education Foundation, Green Fields, Vaddeswaram, Guntur, Andhra Pradesh, India 522502 \*Corresponding Author E-mail: nagababuchakkapalli@gmail.com,

## Abstract

In this paper we compared a high speed carry skip adders by considering parameters such as area, LUT'S, delay, power. When compared to conventional CSKA and other adders. Here in this project in first stage CSKA designed by using multiplexer as skip logic so by using this speed gets increased by skipping of carry. so here area gets increased so to reduce area another hybrid variable latency carry skip adder(Brent-kung adder) is designed .here power utilization also gets decreased, speed gets increased, but some delay is produced here to overcome that we followed a another method called Kogge-Stone adder here so it reduces the critical path delay. In Kogge-stone adder power is highly consumed due to more no of wiring connections so another adder was designed to reduce power consumption which is Sklansky adder which reduces power Consumption. This is done in Xilinx ISE 14.7 and power was analyzed using Xilinx power analyzer.

Keywords: Brent-Kung adder, Skip logic, Kogge-Stone adder, Sklansky adder.

# **1. Introduction**

Adders are an electronic circuit that performs adding of two numbers which produces sum and carry. They are building blocks in VLSI circuits are used in ALU'S and various types of microprocessors. They are used to compute instrumentation or defragmentation of values.

## Types of adders

There are many types of adders like Ripple carry adder, carry select adder, carry bypass adder (also known as CSKA).

### A) Ripple carry adder

A ripple carry adder is combination of two or more full adders by giving  $C_{in}$  as input, so there by carry gets propagated from one full adder to another one by producing sum and  $C_{out}$  as outputs.

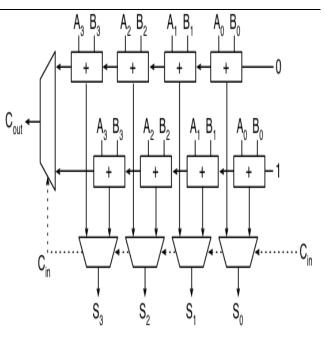

### B) Carry select adder

A carry select adder is combination of two ripple carry adders and a multiplexer. The inputs are given simultaneously to both ripple carry adders and sum of 1<sup>st</sup> ripple carry adder is propagated to 2<sup>nd</sup> one and these sum's of two ripple carry adders are sent through the multiplexer and final sum is calculated.In same way final carry's of the RCA'S are multiplexed and final C<sub>out</sub> is calculated.

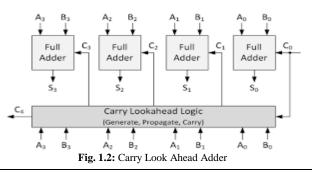

### C) Carry look ahead adder

A carry look ahead adder is fast parallel adder as it reduces more propagation delay by increasing complex hardware.

Fig. 1.1 Carry Select Adder

Copyright © 2018 Authors. This is an open access article distributed under the <u>Creative Commons Attribution License</u>, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

### D) Carry skip adder

A carry skip is one which skips the carry by using combination of full adders, each full adder consists of 3 outputs one is sum another is carry and another is parity and these parity outputs of all full adders are given to skip logic which is combination of AND gate and a multiplexer. The output of the and gate is given as selection line for multiplexer and the inputs of the multiplexer are  $c_{in}$  and  $c_{out}$  based on selection line input  $c_{in}$  or  $c_{out}$  is selected.

Fig. 1.3: Conventional CSKA

# 2. Parallel Prefix adders

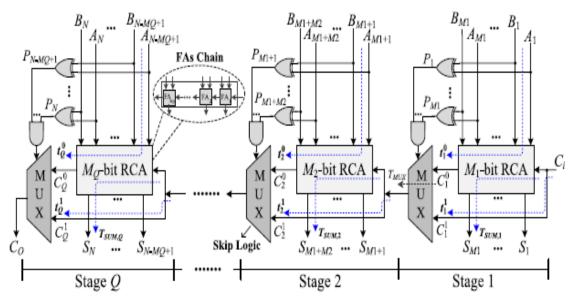

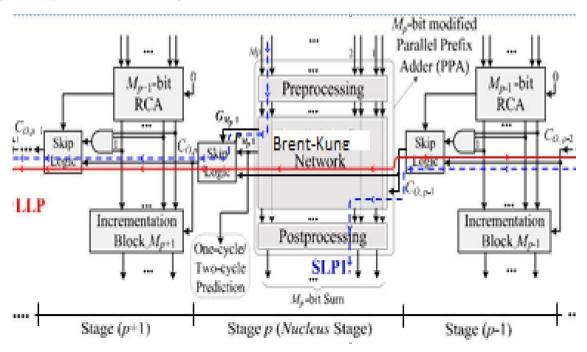

## A) Brent-Kung cska

The idea behind choosing this Brent-kung adder was that the critical path delay gets minimized when compared to conventional

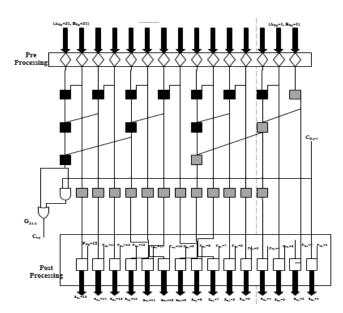

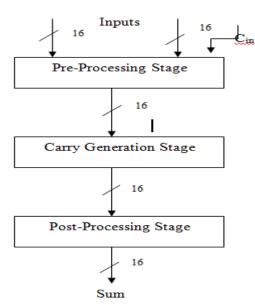

CSKA. So for that we replace some of the middle stages with a Parallel Prefix Adders. The internal structure of Brent Kung adder is shown in above figure 2.2 which contains 3 Stages pre processing stage, carry generation stage, post Processing stage.

Fig. 2.1: Structure of Brent-Kung CSKA

Fig. 2.2: Internal structure of Brent Kung cska

Fig. 2.3: Structure of Brent-Kung adder

In the Brent-Kung cska Black cell works 3 gates and gray cell works in two gates, the gray cell reduces delay because it works only in 2 gates. It consists of three stages, In preprocessing stage generate and propagate equations are obtained by equations.

$$P_1 = A_1 XOR B_1$$

(1)

$$G_1 = A_1 \& B_1$$

(2)

In carry generation stage the equations are formed by

$$\begin{array}{l} C_{p} = P_{1} \& P_{0} \\ C_{g} = G_{1} \parallel (P_{1} \& G_{0}) \end{array} \tag{3}$$

In the post processing stage the carry of the first bit is XOR with to the next bit of propagates ,then the output sum equation is obtained as

$$S_i = P_i \& C_{i-1}$$

(5)

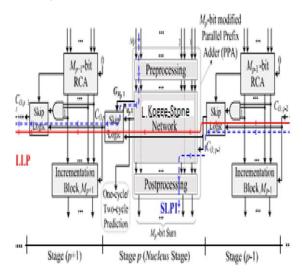

#### B) Kogge-Stone cska

To further reduce delay that is produced by the Brent-Kung the new structure was proposed was that Kogge-Stone adder.it reduces delay to much more extent and area also decreases as well as no of LUT'S also gets decreased. Kogge-Stone is parallel prefix form of carry-look ahead adder.Kogg-stone tree adder reduces the critical path to

$$t_{\text{tree}} = t_{\text{pg}} + [\log_2 N] t_{\text{AO}} + t_{\text{XOR}}$$

(6)

Fig. 2.4: Block diagram of Kogge-Stone cska

Fig. 2.5: Internal structure of Kogge-Stone cska

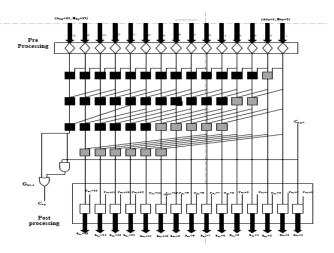

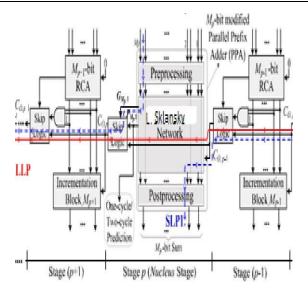

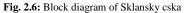

#### C) Sklansky cska

To overcome difficulties in Kogge-Stone new adder was proposed which is Sklansky adder in Kogge-stone adder area occupied is more because of large wiring capacitance hence power consumption also increases. The Sklansky is also known as divide-and-conquer-tree reduces delay to log<sub>2</sub> N stages by computing intermediate prefixes along with larger group prefixes.

Fig. 2.7 Internal structure of Sklansky cska

# **3. Results**

**Comparison Table:**

| Table 3.1: Comparison table |        |         |        |       |

|-----------------------------|--------|---------|--------|-------|

| Adder type                  | Delay  | Power   | Slices | No of |

|                             | (ns)   | (watts) |        | LUT'S |

| CSKA                        | 24.342 | 0.027   | 28     | 48    |

| Brent-Kung                  | 23.094 | 0.023   | 49     | 87    |

| Kogge-Stone                 | 14.45  | 0.032   | 42     | 78    |

| Sklansky                    | 18.85  | 0.023   | 46     | 82    |

Output Wave forms:

Fig. 3.1: Output wave form of CSKA's

The output waveform response of a 4 types of CSKA is same but delay is optimized over four CSKA like Brent Kung, Kogge-stone, and Sklansky CSKA'S

# 4. Conclusion

Analysis of different adders using Xilinx-Verilog programming is done and different parameters like delay, power and LUT's are compared as shown in table 1. From the obtained results it can be said that Kogge stone CSKA is preferred one for the applications where adder has to be implemented as its speed is more compared to conventional CSKA, Brent-Kung CSKA and Sklansky CSKA .The number of LUT's required for implementation of Kogge stone CSKA is also less compared to Brent-Kung CSKA and Sklansky CSKA so that the area can be reduced for hardware implementation of Kogge stone CSKA.

# References

- [1] S. Turrini, "Optimal group distribution in carry-skip adders," in9th Computer Arithmetic Symposium

- [2] Krishna, B. M., Khan, H., Mathematic, G. L., Lohitha, B., Bhavitha, E., Sri, P. T., & Kumar, B. A. (2017). FPGA implementation of DNA based aes algorithm for cryptography applications. International Journal of Pure and Applied Mathematics, 115(7 Special Issue), 525-530.

- [3] Pamula, K., Murali Krishna, B., Mathematic, G.L., & Kanth. (2015). FPGA implementation of multi-bit flip-flop based on power optimization technique. International Journal of Applied Engineering Research, 10(14), 34042-34046.

- [4] Vaidehi, C. S., Murali Krishna, B., Mathematic, G. L., & Kalyan, N. (2014). HDL implementation & performance comparison of various filtering techniques using FPGA. International Journal of Applied Engineering Research, 9(18), 5085-5094.

- [5] Rajesh, J., Muralikrishna, B., Khan, H., & Mathematic, G. L. (2015). Asic implementation of low power nand flash controller with E-MMC interface. International Journal of Applied Engineering Research, 10(10), 25417-25431.

- [6] Abdul, A. M., Krishna, B. M., Murthy, K. S. N., Khan, H., Yaswanth, M., Meghan, G., & Mathematic, G. L. (2016). IOT based home automation using FPGA. Journal of Engineering and AppliedSciences, 11(9), 1931-1937. 10.3923/jeasci.2016.1931.1937.

- [7] Meka Bharadwaj, Hari Kishore "Enhanced Launch-Off-Capture Testing Using BIST Designs" Journal of Engineering and Applied Sciences, ISSN No: 1816-949X, Vol No.12, Issue No.3, page: 636-643, April 2017.

- [8] P Bala Gopal, K Hari Kishore, R.R Kalyan Venkatesh, P Harinath Mandalapu "An FPGA Implementation of On Chip UART Testing with BIST Techniques", International Journal of

Applied Engineering Research, ISSN 0973-4562, Volume 10, Number 14, pp. 34047-34051, August 2015.

- [9] Avinash Yadlapati, Dr. Hari Kishore Kakarla, "An Advanced AXI Protocol Verification using Verilog HDL", Wulfenia Journal, ISSN: 1561-882X, Volume 22, Number 4, pp. 307-314, April 2015

- [10] P Ramakrishna, K. Hari Kishore, "Design of Low Power 10GS/s 6-Bit DAC using CMOS Technology "International Journal of Engineering and Technology(UAE), ISSN No: 2227-524X, Vol No: 7, Issue No: 1.5, Page No: 226-229, January 2018.

- [11] A Murali, K. Hari Kishore, "Efficient and High Speed Key Independent AES Based Authenticated Encryption Architecture using FPGAs "International Journal of Engineering and Technology(UAE), ISSN No: 2227-524X, Vol No: 7, Issue No: 1.5, Page No: 230-233, January 2018.

- [12] G.S.Spandana, K Hari Kishore "A Contemporary Approach For Fault Diagnosis In Testable Reversible Circuits By Employing The CNT Gate Library" International Journal of Pure and Applied Mathematics, ISSN No: 1314-3395, Vol No: 115, Issue No: 7, Page No: 537-542, September 2017.

- [13] K Hari Kishore, CVRN Aswin Kumar, T Vijay Srinivas, GV Govardhan, Ch Naga Pavan Kumar, R Venkatesh "Design and Analysis of High Efficient UART on Spartran-6 and Virtex-7 Devices", International Journal of Applied Engineering Research, ISSN 0973-4562, Volume 10, Number 09, pp. 23043-23052, June 2015

- [14] K Bindu Bhargavi, K Hari Kishore "Low Power BIST on Memory Interface Logic", International Journal of Applied Engineering Research, ISSN 0973-4562, Volume 10, Number 08, pp. 21079-21090, May 2015.

- [15] Korraprolu Brahma Reddy, K Hari Kishore, "A Mixed Approach for Power Dissipation Reduction in Nanometer CMOS VLSI circuits", International Journal of Applied Engineering Research, ISSN 0973-4562 Volume 9, Number 18, pp. 5141-5148, July 2014.

- [16] Nidamanuri Sai Charan, Kakarla Hari Kishore "Reorganization of Delay Faults in Cluster Based FPGA Using BIST" Indian Journal of Science and Technology, ISSN No: 0974-6846, Vol No.9, Issue No.28, page: 1-7, July 2016.

- [17] Sravya Kante, Hari Kishore Kakarla, Avinash Yadlapati,"Design and Verification of AMBA AHB-Lite protocol using Verilog HDL" International Journal of Engineering and Technology, E-ISSN No: 0975-4024, Vol No.8, Issue No.2, Page:734-741, April-May 2016.

- [18] Bandlamoodi Sravani, K Hari Kishore, "An FPGA Implementation of Phase Locked Loop (PLL)", International Journal of Applied Engineering Research, ISSN 0973-4562, Volume 10, Number 14, pp. 34137-34139, August 2015

- [19] Avinash Yadlapati, Kakarla Hari Kishore, "Constrained Level Validation of Serial Peripheral Interface Protocol", Proceedings of the First International Conference on SCI 2016, Volume 1, Smart Computing and Informatics, Smart Innovation, Systems and Technologies 77, ISSN No: 2190-3018, ISBN: 978-981-10-5544-7, Chapter No: 77, pp. 743-753, 25<sup>th</sup> December 2017.

- [20] P Kiran Kumar, P Prasad Rao, Kakarla Hari Kishore, "Optimal Design of Reversible Parity Preserving New Full Adder / Full Subtractor", IEEE SPONSORED 3<sup>rd</sup> INTERNATIONAL CONFERENCE ON ELECTRONICS AND COMMUNICATION SYSTEMS (ICECS 2016), pp. 3465-3470, 25<sup>th</sup> and 26<sup>th</sup> February 2016.

- [21] Y Avinash, K Hari Kishore 'Designing Asynchronous FIFO for Low Power DFT Implementation' International Journal of Pure and Applied Mathematics, ISSN No: 1314-3395, Vol No: 115, Issue No: 8, Page No: 561-566, September 2017.

- [22] Mahesh Mudavath and K Hari Kishore "Design of RF Front End CMOS Cascade CS Low Noise Amplifier on 65nm Technology Process" International Journal of Pure and Applied Mathematics, ISSN No: 1314-3395, Vol No: 115, Issue No: 7, Page No: 417-422, September 2017.

- [23] P. Sahithi K Hari Kishore, E Raghuveera, P. Gopi Krishna "DESIGN OF VOLTAGE LEVEL SHIFTER FOR POWER-EFFICIENT APPLICATIONS USING 45nm TECHNOLOGY" International Journal of Engineering and Technology(UAE), ISSN No: 2227-524X, Vol No: 7, Issue No: 2.8, Page No: 103-108, March 2018.

- [24] N Bala Dastagiri K Hari Kishore "A 14-bit 10kS/s Power Efficient 65nm SAR ADC for Cardiac Implantable Medical Devices" International Journal of Engineering and Technology(UAE), ISSN

No: 2227-524X, Vol No: 7, Issue No: 2.8, Page No: 34-39, March 2018.

- [25] Shaik Razia, P.Swathi Pryathyusha, N.Vamsi Krishna "A Comparative study of machine learning algorithms on thyroid disease prediction" International Journal of Engineering and Technology(UAE), ISSN No: 2227-524X, Vol No: 7, Issue No: 2.8, Page No: 315-319, March 2018

- [26] S RAZIA, "A REVIEW ON DISEASE DIAGNOSIS USING MACHINE LEARNING TECHNIQUES", International Journal of Pure and Applied Mathematics, ISSN No: 1314-3395, Vol No: 117, Issue No: 16, Page No: 79-85, 201

- [27] S Razia, MR Narasingarao, GR Sridhar, "A decision support system for prediction of thyroid disease-a comparison of multilayer perception neural network and radial basis function neural network", Journal of Theoretical and Applied Information Technology, ISSN 1992-8645, Volume 80, No.3, pp.544, 2015.

- [28] S.V.Manikanthan and T.Padmapriya "Recent Trends In M2m Communications In 4g Networks And Evolution Towards 5g", International Journal of Pure and Applied Mathematics, ISSN NO: 1314-3395, Vol-115, Issue -8, Sep 2017.

- [29] S.V. Manikanthan, T. Padmapriya "An enhanced distributed evolved node-b architecture in 5G tele-communications network" International Journal of Engineering & Technology (UAE), Vol 7 Issues No (2.8) (2018) 248-254.March2018.

- [30] S.V. Manikanthan, T. Padmapriya, Relay Based Architecture For Energy Perceptive For Mobile Adhoc Networks, Advances and Applications in Mathematical Sciences, Volume 17, Issue 1, November 2017, Pages 165-179