**International Journal of Engineering & Technology**

Website: www.sciencepubco.com/index.php/IJET doi: 10.14419/ijet.v7i4.13678 **Research paper**

# Design of CSDG MOSFET based low noise amplifier for GHZ range

Lwazi Luthuli\*, Viranjay M. Srivastava

Department of Electronic Engineering, Howard College, University of KwaZulu-Natal, Durban – 4041, South Africa \*Corresponding author E-mail: lwaziluthuli0@gmail.com, viranjay@ieee.org

# Abstract

In this paper we have presented a Cylindrical Surrounding Double-Gate (CSDG) MOSFET based Low Noise Amplifier (LNA) that operates at frequencies from 1 GHz to 10 GHz. The designed CSDG based LNA is combination of conventional LNA with CSDG MOSFET for low noise figure at high frequencies. The CSDG MOSFET comprises of both the main and active feedback transistor. The highest gain achieved is -16 dB at 2.4 GHz. The stability factor K greater than 1 and the achieved lowest noise figure is 0.2 dB at 10 GHz. The proposed designed LNA provides the lowest noise figure at the highest frequencies compared to other conventional LNAs.

Keywords: Cylindrical Surrounding Double-Gate MOSFET; Gain; Noise Figure; Nanotechnology; Microelectronics; VLSI.

# 1. Introduction

In communication systems, Low Noise Amplifier (LNA) amplifies a weak signal without diminishing its signal-to-noise ratio [1]. The purpose of a general analogue electronic amplifier is to increase power of the signal at the input. However, it also increases the noise existing at the input [2]. The LNAs provide a solution to the unwanted amplification of the noise, caused in part by thermal adverse effects, by reducing it while the signal power at the input increases. In a typical communication system, an LNA amplifies the signal that has been received whilst keeping the noise to a minimum [3, 4].

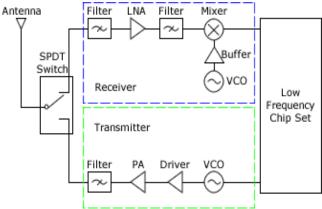

In order to be efficient receiver front-end circuitry in a communication system the LNA has to operate effectively at high frequencies. The performance of a communication relies on effective LNA since the LNA is first gain stage, which amplifies the weak signal received from the antenna [5, 6]. Thus, the designing of low noise amplifier will make vital advances in the performance of wireless communications systems [7].

Fig. 1: Block Diagram of a Communication System with an LNA [5].

In this work an LNA has been designed which has active feedback for improved linearity, stability and low noise figure for high frequency applications (1 GHz to 10 GHz). Both the main transistor and feedback transistor have been replaced with a Cylindrical Surrounding Double-Gate (CSDG) MOSFET to make the novel device.

This work has been organized as follows: Section II describes the basic components used to design this model. Section III has the proposed model with its discussion. Section IV describes the response analysis of this proposed model and behavior at the various frequencies. Finally, the section V concludes the work and recommends the future aspects.

# 2. Basics of components used

### 2.1. Low noise amplifiers

In modern wireless communication systems, the focus is to design the ideal LNA, which has a low Noise Figure and maximum linearity [2, 8, 9]. Bhasin et. al. [10] have designed an LNA where gain was optimized and noise figure was kept minimum. In a similar study an LNA had gain of 31 dB and noise figure of 0.533 dB at frequency of 1.57 GHz. The optimization was achieved by cascading a single ended topology [11]. Kulkarni and Ananthakrishnan [12] analysed the minimization of the noise figure and optimization of the stability through two methods: (i) mismatch in the input impedance matching network for the lowest NF at the cost of gain. Which yielded an NF < 1dB and had a stability factor K > 1, and (ii) considered the NF to be kept constant.

When we introduce inductance at the source of the main transistor this permits series feedback without creating a resistive element. Had the resistive element been created this would adversely affect the NF by increasing it [13]. The NF minimization and stability optimization was for frequencies from 1 GHz to 3 GHz.

In [14] an LNA was presented which was derived from using the derivative superposition method. The linearity improvement

Copyright © 2018 Lwazi Luthuli, Viranjay M. Srivastava. This is an open access article distributed under the <u>Creative Commons Attribution</u> License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

boosts the sensitivity and effectiveness of the LNA [15]. The derivative superposition method and an active MOSFET feedback transistor LNA using this method achieved a third-order input intercept point (IIP3) of 21 dBm, a gain of 9.43 dB and a 2.4 dB optimal NF [16]. These NF minimizations were obtained for an operating frequency of 5.8 GHz.

# 2.2. Cylindrical Surrounding Double-Gate (CSDG) MOSFET Structure

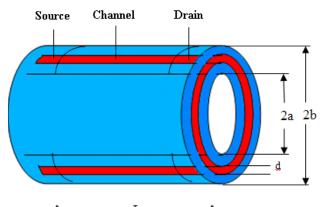

CSDG MOSFET has two gates into a packaged transistor. An analytical model for undoped CSDG MOSFET was proposed in [17] and it was centred on a unified charged control occurrence. It was from this occurrence that allowed them to express a channel in terms of the channel charge densities at the source and the drain ends of the channel [17-19].

Modern advanced MOSFETs cannot be scaled down further since it has reached size limitations in terms of length and width, the Double Gate MOSFET has an increased transconductance and a lower threshold voltage. Both the substances and the inherent thickness of back-oxide and the front oxide layer are the same. This permits both gates to have simultaneous control of the MOSFET. Major advantages of these simultaneous operations are that the channel area is raised to increase the saturation current and Si-body control is improved to minimise adverse short channel effects.

The CSDG MOSFET has the scaling advantage over the bulk MOSFETs and DG MOSFETs, due to its surface area, can be scaled down to twice that of the lowest scale of the bulk MOSFET. In addition to these advantages the CSDG MOSFET has higher channel mobility compared to the conventional MOSFET, due to the average electric field being lower and in-turn reduces the scattering of the charge carriers [20, 21]. Since we have a better performance in double-gate as compared to conventional scaling limited MOSFET, this CSDG MOSFET can also lend itself to conventional MOSFETs applications like RF Low Noise Amplifiers (LNA) for wireless communications.

## 3. Proposed model

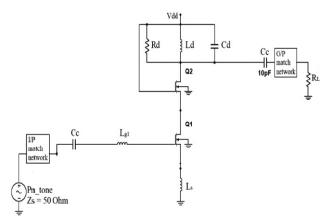

The element of novelty in the proposed LNA is that we replaced both the main transistor and the active feedback transistor with one CSDG MOSFET. In a conventional LNA the main transistor with passive feedback reduces the performance of the LNA by adversely affecting the NF and resulting destabilization due to uncontrolled feedback. Two individual transistors in an LNA (the main and active feedback), are used to improve linearity and have controlled feedback.

Fig. 2: Conventional MOSFET LNA with feedback [16].

**Fig. 3:** Cylindrical Surrounding Double-Gate MOSFET model [17].

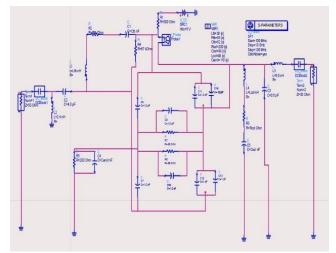

Fig. 4: Cylindrical Surrounding Double-Gate MOSFET Based LNA.

The bulky transistor adversely affects the device because it increases the parasitic capacitance and hence reduces the optimum gain. So, the CSDG MOSFET is an ideal choice since it is in the nano-scale. The size of the CSDG MOSFET is [5] nm thick body, with  $N_A = 10^{20}$  atoms/cc, internal radius, a = 10 nm. With sizes so small the saturation current of a CSDG MOSFET will be larger than that of a DG MOSFET [17]. The CSDG LNA circuit and its individual subsections have been simulated in a circuit simulator. The design of the CSDG MOSFET LNA has been achieved by replacing the feedback transistor and the main transistor in Fig. 2 in an LNA with one transistor. It has two gates as its input (CSDG) in Fig 3. The final design circuit has the active feedback and main transistor is replaced by a designed CSDG as shown in Fig. 4.

# 4. Analysis and results

#### 4.1. Gain

For a LNA the ratio of power at the output  $(P_{out})$  of the amplifier to the power at the input  $(P_{in})$  is known as gain. Since the noise present in the signal is also amplified along with the weak signal, so we have tried to reduce the noise by increasing the gain. This has been achieved with the help of impedance matching at the input and the output [22, 23]:

$$Gain = \frac{P}{\frac{Out}{P_{in}}}$$

(1)

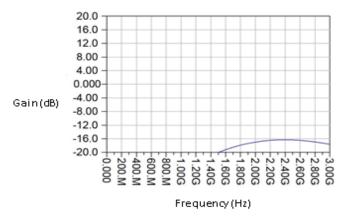

Fig. 5: Gain of CSDG LNA.

The CSDG MOSFET based LNA has been simulated in the range of 1 GHz to 10 GHz. The main parameters of interest are the gain, NF, and stability. For a suitable LNA high gain, low NF, and high value of K indicates strong stability.

The highest gain obtained in the frequency range of interest is -16 dB at a frequency of 2.4 GHz. At frequencies, less than 1.5 GHz the gain of the LNA degrades rapidly to less than -20 dB. This rapid degradation is because at high frequencies noise and gain have an inversely proportional relationship. The gain could be improved having N<sup>th</sup> order stage cascaded LNA, possibly of up to three stages would at least double the gain.

The graph in Fig. 5, represents the gain in decibels versus the frequency. The proposed CSDG LNA produced a parabolic waveform of the gain in the frequencies of 1 GHz up to 3 GHz. The minimum gain is between 1 GHz and 20 dB and the maximum gain is -16 dB and is 36 dB less than [11], 26 dB less than [12] and less 25.43 dB [16]. At higher frequencies gains of degraded significantly compared to the CSDG LNA gain [11, 12].

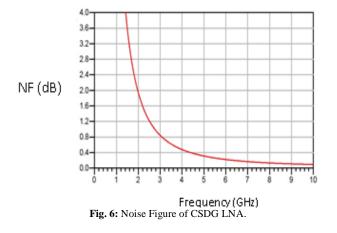

## 4.2. Noise figure (NF)

An increase in NF at high frequencies corresponds to a reduction in the gain. The noise figure is a parameter of the performance of an LNA, which is a strong indication of how much noise is in the received signal. This is useful to know to determine how much noise to remove in a distorted signal at the receiver in a communication system. This factor is a measure of the weakening of a signal in the signal power to noise power ratio between the input and the output [12, 24, 25].

$$NF = \left(\frac{P_{si}}{P_{ni}}\right) \left/ \left(\frac{P_{so}}{P_{no}}\right)$$

(2)

Where  $P_{si}$  and  $P_{so}$  are the power of signal at the input and output, respectively, and  $P_{ni}$  and  $P_{no}$  are the power of noise at the input and output, respectively.

The highest NF of the designed LNA appears at frequencies lower than 2.4 GHz rendering the LNA useless since the NF is high and greater than 4 dB. A typical acceptable NF for a conventional LNA should be less than 1 dB at this frequency. In the frequency of interest, the lowest NF achieved at 10 GHz and is 0.2 dB, 0.8 dB less than the typically acceptable NF for a conventional LNA. This very low NF at a high frequency caused a reduction in the gain as shown in Fig 6. This is a graph of the noise figure versus frequency. The NF waveform is one of an exponentially decaying behavior as the frequency increases from 1.5 GHz to 10 GHz. The lowest NF occurred at 10 GHz and is 0.2 dB compared to other studies the NF, of the CSDG of 0.2 dB, was 0.333 dB less than [11], 0.78 dB less than [12] and 2.2 dB less than [16]. The NF obtained in this work is 45% better than [11], 80% better than [12] and 84.6% better than [16].

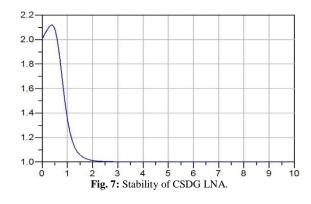

#### 4.3. Stability

Another significant performance parameter which indicates the steadiness or control the LNA has particularly when operating at high frequencies where there is bound to be less control. This parameter is used to check if an LNA is unconditionally stable. This parameter is denoted by K where if we have stability K greater than 1 then we can say the LNA is stable but if K is less than 1 we have instabilities [12, 26 - 29]. The value of K is expressed in terms of S parameters

$$K = \frac{\left(1 + \left|S_{11}\right|^2 - \left|S_{22}\right|^2 - \left|\Delta\right|^2\right)}{2\left|S_{12}S_{21}\right|} \tag{3}$$

Where

$$\Delta = S_{11}S_{22} - S_{12}S_{21}$$

The largest stability occurs for frequencies that are less than 2 GHz, here K is greater than 1 but less than 2.1 and in this range authors also have the gain being fairly high as in Fig 7. However, as the gain degrades for the higher frequencies so too does the stability which is depicted in Fig 7. As we increase the frequency to 10 GHz the stability is just barely acceptable as the value of K approaches 1. The graph for the value K versus frequencies is shown in Fig. 7. From 0 GHz to 1 GHz there is as parabolic relationship between K and the frequency and the maxima is the highest K value of 2.2 at 500 MHz. From 2 GHz to 10 GHz the K value is exactly 1 indicating marginal stability compared to the stability of [11, 12, 16] which have slightly higher K values.

Table 1: Comparison of CSDG LNA with other LNAs.

| Low Noise Amplifier      | Frequency | Gain | Noise Figure |

|--------------------------|-----------|------|--------------|

| (LNA)                    | (GHz)     | (dB) | (dB)         |

| CMOS LNA [11]            | 1.57      | 31   | 0.533        |

| Wideband LNA [12]        | 3         | 10   | 0.98         |

| Active feedback LNA [16] | 5.8       | 9.43 | 2.4          |

| CSDG LNA (this work)     | 10        | -16  | 0.2          |

# 5. Conclusions and future recommendations

The Cylindrical Surrounding Double-Gate MOSFET based Low Noise Amplifier has been designed and simulated in the frequency range of 1 GHz to 10 GHz. The design has the combination of conventional LNA and CSDG MOSFET. The highest gain of the designed LNA is -16 dB. The lowest NF occurred at 0.01 THz and is 0.2 dB. Stability was obtained by the LNA as K approaching at high frequencies. This CSDG MOSFET based LNA design has NF 0.33 dB lower than the LNA in ref. [11] which was 0.53 dB at a frequency of 1.57 GHz. This designed LNA also has a NF that is 2.2 dB lower than the LNA in ref. [16] which was 2.4 dB minimum NF at 5.8 GHz.

The designed LNA has the lowest NF at the highest frequency compared to the mentioned LNAs. Use of the CSDG MOSFET reduced the NF considerably compared to existing large bulky MOSFET LNAs, which was one of the reasons it was incorporated into the design for its anticipated reduction in the NF. The LNA can be used in wireless communication systems operating at frequencies of up to 10 GHz and have a low NF.

Possible future work would be to have a multi-stage CSDG LNA that can improve both the NF and the gain at high frequencies. We can also consider a feedback CSDG MOSFET added to improve the linearity and to achieve the better stability at high Frequencies.

# References

- [1] Bill Smith, *Electronic amplifiers and circuit design*, Wexford College Press, Sept. 2009.

- [2] Roberto Diaz Ortega and Sunil Lalcand Khemchandani, Design of Low-Noise Amplifiers for Ultra-Wideband Communications, McGraw-Hill Education, USA, Jan. 2014.

- [3] Akanksha Sahu, Paresh C. Sau, and Dheeraj Kalra, "Design of low power UWB LNA for frequency 3.1–5 GHz in 0.18 μm CMOS technology," *Int. Conf. on Computing, Communication and Automation (ICCCA)*, Noida, India, 15-16 May 2015, pp.198-201. https://doi.org/10.1109/CCAA.2015.7148371.

- [4] Fedrerico Bruccoleri, Eric A. M. Klumperink, and Bram Nauta, Wideband low noise amplifiers exploiting thermal noise cancellation, Springer, USA, 2005.

- [5] Frank Gross, Smart antennas for wireless communications, with MATLAB, 1<sup>st</sup> Ed., McGraw-Hill, Sept. 2005.

- [6] Constantine A. Balanis, Modern Antenna Handbook, John Wiley & Sons, USA, Sept. 2008.

- [7] Thomas H. Lee, *The design of CMOS radio frequency integrated circuits*, 2<sup>nd</sup> Ed., Cambridge University Press, Cambridge, UK, 2004.

- [8] Ramkrishna Kundu, Abhishek Pandey, Subhra Chakraborty, and Vijay Nath, "A CMOS low noise amplifier based on common source technique for ISM band application," *Microsystem Technol*ogy, vol. 22, no. 11, pp 2707–2714, Nov. 2016. https://doi.org/10.1007/s00542-015-2550-3.

- [9] Louis J. Ippolito, Satellite communication systems engineering: atmospheric effects, satellite link design and system performance, pp. Wiley, 2<sup>nd</sup> Ed., May 2017.

- [10] Himanshu Bhasin, Sandeep Kumar, Santanu Dwari, Mitul Handa, and Binod K. Kanaujia, "Optimization of noise figure and gain of a CMOS RF low noise amplifier" 9<sup>th</sup> Int. Conf. on Industrial and Information Systems (ICIIS), Gwalior, India, 15-17 Dec. 2014, pp. 1-4. https://doi.org/10.1109/ICIINFS.2014.7036644

- [11] Namrata Yadav, Abhishek Pandey, and Vijay Nath, "Design of CMOS low noise amplifier for 1.57GHz," Int. Conf. on Microelec-

tronics, Computing and Communications (MicroCom), Durgapur, India, 23-35 Jan. 2016, pp. 1-5. https://doi.org/ 10.1109/MicroCom.2016.7522438

- [12] Abhay P. Kulkarni and S. Ananthakrishnan, "1 to 3 GHz wideband low noise amplifier design," 5<sup>th</sup> Int. Conf. on Computers and Devices for Communication (CODEC), Kolkata, India, 17-19 Dec. 2012, pp. 1-4. https://doi.org/ 10.1109/CODEC.2012.6509335

- [13] Dale D. Henkes, "LNA design uses series feedback to achieve simultaneous low input VSWR and low noise," *Applied Microwave & Wireless*, pp. 26-32, October 1998.

- [14] Vladimir Aparin and Lawrence E. Larson, "Modified derivative superposition method for linearizing FET low noise amplifiers," *IEEE Trans. of Microwave Theory and Techniques*, vol. 53, no. 2, pp. 571-581, Feb. 2005. https://doi.org/10.1109/TMTT.2004.840635.

- [15] L. Ma, Z. G. Wang, and J. Xu, "A high linearity wideband common gate LNA with differential active inductor," *IEEE Trans. Circuits Syst. II*, Express Briefs, vol. 64, no. 4, pp. 402-406, April 2017. https://doi.org/10.1109/TCSII.2016.2572201.

- [16] Farooq A. Khaleel and Mohammed N. Abbas, "Tunable linearity enhancement for 180 nm complementary metal-oxidesemiconductor LNA with active feedback" *The Journal of Engineering*, vol. 2017, no. 7, pp. 312-317, July 2017. https://doi.org/10.1049/joe.2017.0067

- [17] Viranjay M. Srivastava, K. S. Yadav, and G. Singh, "Design and performance analysis of cylindrical surrounding double-gate MOSFET for RF switch," *Microelectronics Journal*, vol. 42, no. 10, pp. 1124-1135, Oct. 2011. https://doi.org/10.1016/j.mejo.2011.07.003.

- [18] Viranjay M. Srivastava, K. S. Yadav, and G. Singh, "Analysis of double gate CMOS for double-pole four-throw RF switch design at 45-nm technology," *J. of Computational Electronics*, vol. 10, no. 1-2, pp. 229-240, June 2011. https://doi.org/10.1007/s10825-011-0359-6.

- [19] Viranjay M. Srivastava and G. Singh MOSFET Technologies for Double-Pole 4 Throw Radio Frequency Switch, Springer International Publishing, Switzerland, Oct. 2013.

- [20] Tao Chuan Lim and G. Alastair Armstrong, "Scaling issues for analogue circuits using Double Gate SOI transistors," *Solid-State Electronics*, vol. 51, no. 2, pp. 320-327, Feb. 2007. https://doi.org/10.1016/j.sse.2007.01.006.

- [21] S. Kang and Yusuf Leblebichi, CMOS Digital Integrated Circuits Analysis & Design, 3rd Ed., McGraw-Hill, New York, USA, 2002.

- [22] Gabriele Manganaro and Domine Lenaerts, Advances in analogue and RF IC design for wireless communication systems, Elsevier, 1<sup>st</sup> Ed., May 2013.

- [23] Robert Sobot, Wireless communication electronics: Introduction to RF circuits and design techniques, Springer-Verlag, New York, 2012. https://doi.org/10.1007/978-1-4614-1117-8.

- [24] Dave Adamy, Practical Communication Theory (Electromagnetics and Radar), 2<sup>nd</sup> Ed., SciTech Publishing, Aug. 2014.

- [25] Fraidoon Mazda, *Telecommunications engineer's reference Book*, Butterworth Heineman, 1993.

- [26] Art Kay, Operational amplifier noise: Techniques and tips for analyzing and reducing noise, Elsevier, 1<sup>st</sup> Ed., Jan. 2012.

- [27] Ian A. Glover, Steve Pennock, and Peter Shepherd, Microwave devices, circuits and subsystems for communications engineering, Wiley, May 2005.

- [28] Andrei Grebennikov, *RF and microwave power amplifier design*, McGraw Hill, USA, 2005.

- [29] Guillermo Gonzalez, Microwave transistor amplifiers analysis and design, 2<sup>nd</sup> Ed., Prentice Hall, New Jersey, USA, 1996.