**International Journal of Engineering & Technology**

Website: www.sciencepubco.com/index.php/IJET doi: 21417 **Research naner**

# A low pass filter based integrator in a digital feedback loop AGC for WLAN receivers

Bharath H. P<sup>1</sup>\*, P. I. Basarkod<sup>1</sup>

<sup>1</sup>School of ECE, REVA University, Bangalore \*Corresponding author E-mail: bharath.hp@reva.edu.in

### Abstract

This paper describes a Digital feedback loop automatic gain control (AGC) for Wireless Local Area Network (WLAN) receivers. The proposed AGC employs a novel lowpass filter-based integrator for the gain generation, which controls digital multiplier to maintain constant signal dynamic range. The AGC performance is analyzed for 16 and 64 Quadra-ture Amplitude Multiplexing-Orthogonal Frequency Division Multiplexing (QAM-OFDM) modulated signal with differ-ent attenuation factors under Additive White Gaussian Noise (AWGN) channel. The proposed AGC has a dynamic range of 70dB with the gain error less than  $\pm 1$ dB and settling time is 1.2µs. The proposed algorithm is validated on a Field Programmable Gate Array (FPGA) platform.

Keywords: Automatic Gain Control; Quadrature Amplitude Multiplexing; Wireless Local Area Network; Feedback AGC.

## 1. Introduction

The AGC is an essential block in WLAN receivers to maintain the constant dynamic range of the received signal. There are different standards for wireless communications such as 802.11a/b/g standards, which operates over different capacity and range of coverage for wireless access. Most of these communication standards use OFDM modulation to employ high data rates in the multipath channel environment. In WLAN protocol, each received data packet consists of a preamble, header and data segments. The preamble consists of ten short training symbols of 0.8  $\mu$ s and two long training symbols of 4 $\mu$ s each. During the preamble duration, AGC must amplify or attenuate incoming signal without altering its envelope. WLAN modem employs M-ary QAM-OFDM modulation technique, in which the message is coded in both amplitude and phase of the carrier signal. This short preamble time which arrives in burst communication mode poses a challenge in AGC response.

There have been several research contributions that provide AGC algorithms and discussed the implementation issues. In [1][5][7] a single stage Digital AGC is proposed to control the gain of coarse Programmable Gain Amplifier (PGA) [6] and fine Low Noise Amplifier (LNA) with the help of Digital to Analog Converter for full band cable receiver application. In [2][8][10] a feedback digital AGC algorithm, which controls the update moment of AGC by the feedback of acquisition and tracking state to eliminate the effect of amplitude fluctuation in DSSS receiver, is proposed. In [4-6] presented a new feedback analog AGC algorithm using switched coarse gain steps, followed by an analog open-loop fine gain step to set the gain of VGAs for WLAN receiver. In these papers, a separate AGC for coarse and fine gain adjustments are discussed, which results in hardware complexity and results are provided without considering hardware implementation constraints. In analog AGC, the presence of R-C components in energy estimator will affect loop gain and settling time. Hence analog AGC loop [11-14] will limit the performance of digital burst modes communication protocol-based receivers such as Bluetooth and WLAN applications. This work focuses on the design and analysis of Digital AGC algorithm for QAM-OFDM modulation technique for 802.11b receivers with operating frequency band 2.4GHz. The proposed architecture has a feedback loop with low pass filter-based integrator for adaptive gain control. The AGC has a dynamic gain range of 70dB with gain steps of 1dB. The algorithm is simulated on MATLAB-SIM-ULINK by considering M-ary QAM-OFDM signal with attenuation factors of 20dB, 40dB and 60dB under AWGN channel. The algorithm is validated on FPGA platform in fixed point notation for a 16 and 64-QAM signals. The results are evaluated in terms of Error Vector Magnitude (EVM) by considering QAM constellation under different attenuation factors.

The paper organization is as follows. In section 2, the design of Digital AGC for WLAN Receiver is illustrated. In section 3, the design of low pass filter for feedback loop AGC is discussed. In section 4, Simulation Results of Proposed AGC is presented and carried out performance evaluation. In section 5 hardware implementation results for proposed AGC is shown and in section 7, a few conclusions on this paper is illustrated.

## 2. Design of digital automatic gain control

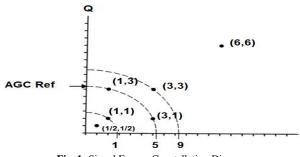

Presence of the communication channel leads to amplitude variations in a signal at the receivers. Fig.1 illustrates the energy constellation plot of the received QAM samples. The constellation point (3, 3) and (1, 1) is having an energy of 9 and 1 respectively. The energy level 1 and 9 are away from the AGC reference value 5. AGC must perform suitable amplitude correction on these energy levels 1 and 9 with respect to AGC reference value, before sending to a demodulator for error-free demodulation of data.

Copyright © 2018 Bharath H. P. P. I. Basarkod. This is an open access article distributed under the Creative Commons Attribution License, which permits unrestricted use, distribution, and reproduction in any medium, provided the original work is properly cited.

Fig. 1: Signal Energy Constellation Diagram.

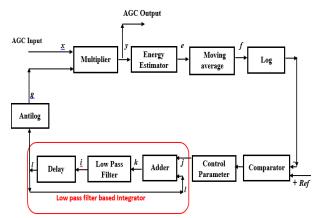

In QAM-OFDM signal, digital bits are encoded into amplitude and phase of the carrier signal. AGC at the receiver must keep received signal at a constant level without changing its message envelope. The important block of the Digital AGC is Multiplier, which amplifies the incoming signal based on gain provided by AGC loop. The presence of multiplier will introduce amplitude modulation (AM) effect at the AGC output, which has not been considered by previously mentioned contributions. To minimize this AM effect, a novel Digital feedback AGC algorithm with lowpass filter-based integrator is proposed as shown in Fig. 2.

Fig. 2: Proposed Architecture of Proposed Digital AGC for WLAN Architecture.

x[n] is AGC [15] input sample multiplied with its corresponding gain sample g[n] to produce AGC output sample y[n + 1]. Where ncorresponds to received signal sample index. In this work we are considering multiplier as amplifier in digital domain.

y[n+1] = x[n] \* g[n] (1)

Energy e[n] of the AGC output sample is computed as

$$e[n] = (Re(y[n]))^{2} + (Imag(y[n]))^{2}$$

(2)

Where Re(y([n])) is in phase component and Imag(y[n])) is Quadrature Phase component of the received QAM sample. To avoid abrupt variations in e[n] we are employing moving average f[n] of energy samples. The Moving averagef[n] of the energy is computed as

$$f[n] = (\frac{1}{k}) \sum_{s=0}^{k} (e_s[n])$$

(3)

Where k=16, k is the moving average window length of the energy samples. The averaged energy value is compared with AGC Ref=0.5V value and multiplied with control parameter (step size) value  $\alpha = 0.1$ ,  $\alpha$  value is AGC gain steps, hence  $\alpha$  must be selected by considering settling time of AGC loop and EVM of AGC output constellation. Output of the control parameter is described as

$$j[n] = \alpha * (\text{Ref} - \log(f[n]))$$

(4)

The output of the control parameter block j[n] is fed to a novel low pass filter-based integrator to produce AGC gain g[n].

$$\mathbf{k}[\mathbf{n}] = \mathbf{l}[\mathbf{n}] + \mathbf{j}[\mathbf{n}] \tag{5}$$

$$\mathbf{l}[\mathbf{n}] = \mathbf{k}[\mathbf{n}] * \mathbf{h}[\mathbf{n}] \tag{6}$$

$$g[n] = \exp(l[n-1]) \tag{7}$$

g[n] is the delayed version of the lowpass filter output l[n]. h[n] is the impulse response of the low pass filter.

#### 3. Design of digital low pass filter for DAGC

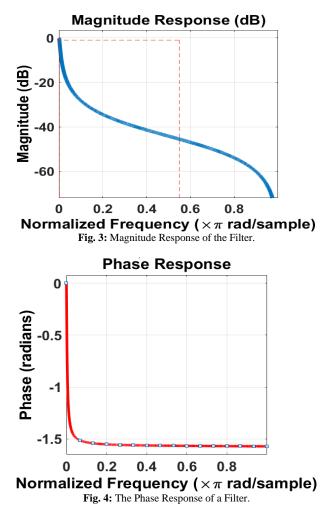

Low pass filter has normalized passband frequency of  $F_p = 0.002$ and normalized stopband frequency of  $F_s = 0.55$ , order of the filter N=1, with passband ripple  $\Omega_p = 1$ dB and with direct form-1 filter structure. The digital low pass filter is designed and analyzed using Filter Visualization (FV) tool of Simulink. The magnitude response of the digital lowpass filter is as shown in the below Fig. 3 and phase response is shown in Fig. 4. The digital low pass filter is iterationbased design, considering AGC loop settling time and % EVM of the QAM constellation as a highest priority. The tarnsfer function of low pass filter in feedback loop DAGC is given by

$$H = \frac{(0.006136Z^2 + 0.006136Z + 1.362x10^{-4})}{(Z^2 - 0.9877Z)}$$

(8)

The magnitude response and phase response of the low pass filter is defecated in Fig. 3 and Fig. 4 respectively.

## 4. Analysis of the proposed DAGC

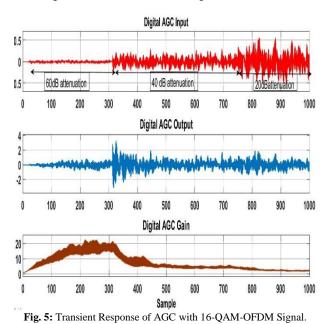

AGC is provided with 16, 64-QAM-OFDM modulated signal with 20 dB, 40 dB and 60 dB attenuation factors to evaluate the performance of the proposed AGC algorithm as shown in Fig. 5. AGC will utilize 200 samples to reach its reference voltage level and corresponding gain is plotted in Fig. 5. The AGC will alter the gain of the digital amplifier based on the incoming signal amplitude to maintain constant output. If the incoming signal amplitude is less than AGC reference value, then AGC will increase the digital amplifier gain to maintain the desired output level.

A 16-QAM-OFDM signal with amplitude with attenuation of 20 dB, 40 dB and 60 dB is applied to AGC with AGC reference value of 0.5V. AGC will compare its input n<sup>th</sup> sample energy with AGC reference value to generate the corresponding gain, which is then applied to (n + 1)<sup>th</sup> sample. The settling time of the proposed AGC is 1.2µs. The gain steps are set to 0.5 dB by choosing the control parameter ( $\alpha$ ) value. The Transient response of the AGC, with corresponding input and gain signals are shown in Fig. 5. In the received samples, 0-300 input samples are of 60 dB attenuation, 300-750 samples are of 40 dB attenuation and 750-1000 samples are of 20 dB attenuation. AGC will generate the gain signal by comparing incoming signal amplitude with its reference value by using sample-based approach. The 60 dB attenuated signal needs amplification gain of 20(13 dB) to settle to its reference value, 40 dB attenuated signal needs the gain of 5(7 dB) and 20 dB attenuated signal needs the gain of 2(3 dB) as shown in Fig. 5.

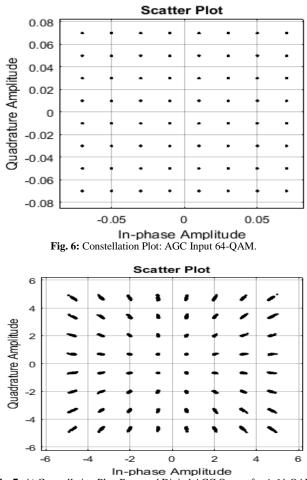

The 64-QAM attenuated signal which is of range 0.08V is fed to AGC, the constellation plot of the signal is shown in Fig. 6. AGC must compensate the attenuations on a received signal and amplify the applied 64-QAM signal. AGC must perform this task without altering the scale of the constellation by restricting an Error Vector Magnitude (EVM) to 10% for error free QAM demodulation as shown in Fig. 7a. The Proposed AGC amplifies the 64-QAM signal by maintaining the 10% EVM compared to conventional Digital

AGC as shown in Fig. 7b.

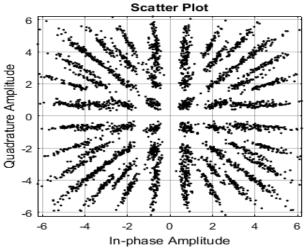

Fig. 7: A) Constellation Plot: Proposed Digital AGC Output for A 64-QAM Signal.

Fig. 7: B) Constellation Plot: Conventional Digital AGC Output for A 64-QAM Signal.

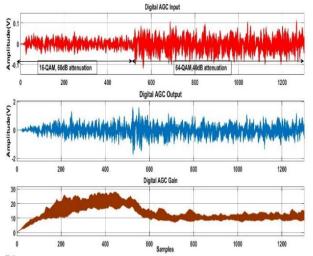

The proposed AGC algorithm is also validated for adaptive modulation technique-based signal by considering, 16-QAM-OFDM and 64-QAM-OFDM signal with an attenuation factor of 60 dB and 40 dB respectively, as shown in Fig. 8. The AGC will maintain output signal at the constant amplitude despite a change in modulation scheme and attenuation factor, hence the proposed AGC is suitable for adaptive modulation-based WLAN receivers.

Fig. 8: Transient Response of the AGC for Adaptive Modulation-Based Signal.

## 5. Experimental results for proposed DAGC

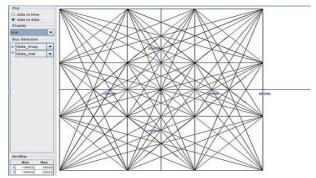

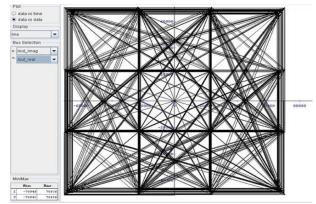

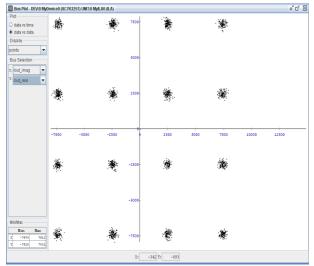

Proposed AGC algorithm results are validated on Kintex-7 FPGA development board. The algorithm is implemented in fixed data point notation on FPGA with the help of a system generator tool. The in-phase(data\_real) data v/s quadrature phase(data\_iimag) data represented in data v/s data mode. The 40 dB attenuated 16-QAM signal take the range from -40000 to +40000 in fixed point notation as shown in constellation plot at Fig. 9. The constellation diagram in Fig. 9 indicates the state transition from one symbol point to another symbol point. The AGC has to follow these transition between the data symbol point while changing the gain of the incoming signal by maintaining the scale of the constellation. The AGC output constellation plot is shown in Fig.10, whose scale has changed to -70000 to + 70000 after the amplification of the QAM signal.

Fig. 9: AGC Input 16-QAM Constellation on Hardware in Chipscope Bus Plot.

Fig. 10: AGC Output 16-QAM Constellation on Hardware in Chip Scope Bus Plot.

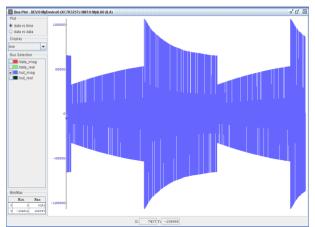

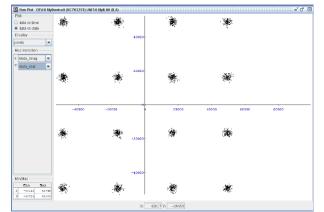

AGC input signal with two attenuation factors is shown below Fig.11, in data v/s time format and its corresponding AGC output is shown in Fig. 12. The proposed AGC algorithm is validated for signal under the presence of AWGN channel with different Signal to Noise (SNR). The attenuated signal constellation of 16-QAM with 20 dB SNR will fall between the scale of 7500 as shown in Fig. 13. AGC will calculate and increase the strength of the QAM constellation signal, which takes the scale of 50000 as shown in Fig. 14.

Fig. 11: AGC Input Signal on Hardware in Chip Scope Bus Plot in Data  $\dot{V}/S$  Time Mode.

**Fig. 12:** AGC Output Signal on Hardware in Chip Scope Bus Plot in Data v/s Time Mode.

Fig. 13: AGC Output16-QAM Constellation with SNR 20 Db on Hardware in Chip Scope Bus Plot in Data v/s Data Mode.

Fig. 14: AGC Output 16-QAM Constellation with SNR 20 Db on Hardware in Chip Scope Bus Plot in Data v/s Data Mode.

#### 6. Conclusion

This paper presents a wide dynamic range low pass filter-based integrator in digital AGC loop for WLAN receivers. The proposed feedback Digital AGC has a dynamic range of 70dB with a gain error less than  $\pm$  1dB which meet the requirement of WLAN receivers. A novel AGC algorithm with a lowpass filter-based integrator is used to eliminate the overshoot effects caused by conventional AGC. The design is analyzed by considering 16, 64 QAM-OFDM signals with different attenuation factors. Validation of design is also carried out on Kintex-7 FPGA platform, which yield EVM less than 10% of the loop settling time, less than 1.2µs. hence the proposed AGC is more suitable for WLAN receivers.

#### References

- Jiangfeng Wu, Giuseppe Cusmai, Acer Wei-Te Chou et al, (2016, April). A 2.7 mW/Channel 48–1000 MHz Direct Sampling Full-Band Cable Receiver, In *IEEE Journal of solid-state circuits*, Vol. 51, No. 4, (pp. 213-215).

- [2] Shen Yuyao, Wang Yongqing, Sheng Dewey, Wu Siliang. (2015, February). Digital AGC Based on Coherent Adjustment Cycle for DSSS Receiver. In *China Communications*, Vol. 12, No. 2, (pp. 95-106). https://doi.org/10.1109/CC.2015.7084405.

- [3] Okjune Jeon, Robert M. Fox, Brent A. Myers. (2006- October). Analog AGC Circuitry for a CMOS WLAN Receiver. In IEEE Journal of Solid-State Circuits, Vol. 41, No. 10, pp. 2291-2300, Oct. 2006. https://doi.org/10.1109/JSSC.2006.881548.

- [4] Sagar Ray, Mona Mostafa Hella. (2016, February). A 10 GB/s Inductor less AGC Amplifier with 40 dB Linear Variable Gain Control in 0.13 μm CMOS. In *IEEE Journal of Solid-State Circuits*, Vol. 51, No. 2, (pp. 440-456). https://doi.org/10.1109/JSSC.2015.2496782.

- [5] Tingting Mo, Jianjun Zhou. (2012, November). Reconfigurable Dual-Channel Multiband RF Receiver for GPS/Galileo/BD-2 Systems. In *IEEE Transactions on Microwave Theory and Techniques*, Vol. 60, No. 11, (pp. 3491-3501). https://doi.org/10.1109/TMTT.2012.2216287.

- [6] Thangarasu Bharatha Kumar, Kaixue Ma, Kiat Seng Yeo. (2012-November).7.9-mW 5.6-GHz Digitally Controlled Variable Gain Amplifier with Linearization, In *IEEE Transactions on Microwave Theory and Techniques*, Vol. 60, No. 11, (pp. 3482-3490). https://doi.org/10.1109/TMTT.2012.2217151.

- [7] Wang Jingdian, LU Xiuhong, Zhang Li. (2018, December). Modeling of a Multiple Digital Automatic Gain Control System, *In Tsinghua Science and Technology*, Vol. 13, No. 6, (pp. 807-811). https://doi.org/10.1016/S1007-0214(08)72204-1.

- [8] E. Tisserand and Y. Berviller. (2016, October). Design and Implementation of a New Digital Automatic Gain Control. In *Electronics Letters*, Vol. 52, No. 22, Apr. 2016 (pp. 1847-1849). https://doi.org/10.1049/el.2016.1398.

- [9] Di Lin, Yin-Tang Yang, Zhan Jing, Zuo-Chen Shi, Yang Liu. (2014, January). A fully integrated feedback AGC loop for ZigBee (IEEE 802.15.4) RF transceiver applications. In *Microelectronics Journal*, *Elsevier*, Vol. 45, (pp. 657-665).

- [10] Y.J. Zheng, J.N. Yan, Y.P. Xu. (2008, December). A CMOS VGA with DC offset cancellation for direct- conversion receivers", In *IEEE Trans. Circuits Systems*, Vol. 56, No. 1, (pp. 103-113).

- [11] Sunyoung Ki, Namjun C ho, Seong-Jun Song, and Hoi-Jun Yoo. (2007, October). A 0.9 V 96 W Fully Operational Digital Hearing Aid Chip. In *IEEE Journal of Solid-State Circuits*, Vol. 42, No. 11, (pp. 2432-2440).

- [12] Xiaoman Wang, Baoyong Chi, Zhihua Wang. (2010, January). A Low-Power High-Data-Rate ASK IF Receiver with a Digital-Control AGC Loop. In *IEEE Transactions on Circuits and Systems*, Vol. 57, No. 8, (pp. 617-621).

- [13] Hsin Wang, Shen-Iuan Liu. (2008, March). 0.18-µm CMOS 1.25-Gbps Automatic-Gain-Control Amplifier. In *IEEE Transactions on Circuits and Systems-II: Express Briefs*, Vol. 55, No. 2, (pp. 136-140).

- [14] Di Li, Yin Tang Yang, Zhan Jing, Zuo Chen Shi, Yang Liu. (2014, May). A fully integrated feedback AGC loop for ZigBee (IEEE 802.15.4) RF transceiver applications. In *Microelectronics Journal*, *Elsevier*, Vol. 45, (pp. 657-665).

- [15] E. Tisserand and Y. Berviller. (2016, Oct). Design and implementation of a new digital automatic gain control. *Electronics Letters*, Vol. 52, No. 22, (pp. 1847–1849). https://doi.org/10.1049/el.2016.1398.